## SERIES 40 MULTICHANNEL ANALYZER

Operator's Manual Revised July, 1983

## SERIES 40 MULTICHANNEL ANALYZER

Operator's Manual Revised July, 1983

### Addition to the Series 40 Operator's Manual

Appendix A.1:

Add -

For domestic operation at 220 volts, the supplied power cord should be replaced with a Underwriters' Laboratories listed, 220 volt-compatible power cord, such as Belden's part number 17566.

Change Table A.1 -

100/120 V fuse rating from 2 A slow-blow to 1.5 A slow-blow. 200/240 V fuse rating from 1 A slow-blow to 0.75 A slow-blow.

## **Table of Contents**

|              |                                 | Page       | 6.     | INPUT/OUTPUT                           | age          |

|--------------|---------------------------------|------------|--------|----------------------------------------|--------------|

| 1.           | INTRODUCTION                    | 4          |        | Data Readout                           | 10           |

| 1.1          | General Description             | . !        | 6.1    | Cassette Recorder I/O                  |              |

| 1.2          | Applications                    | . 2        | 6.2    | Playback of Data                       |              |

| _            |                                 |            | 6.3    | Talatura I/O                           | 20           |

| 2.0 ·        | BASIC SERIES 40 OPERATION       | -          | 6.4    | Teletype I/O                           | 20           |

| 2.1          | Power On                        | . ວ        | 6.5    | Alphánumeric Data ID                   | 21           |

| 2.2          | System Initialization           |            | 6.6    | Recycle                                | . <u>~</u> ! |

| 2.3          | Basic Dialogue Procedures       | . 5        | 6.7    | Model 4251 X-Y Plotter                 | . 41         |

| 2.4          | LED Indicators                  |            | 6.8    | Model 4253 Graphics Plotter            | . 23         |

| 2.5          | Signal Connectors               | . 6        | ***    | ANALYOIO OPTIONO                       |              |

| 2.6          | Gate                            |            | 7.     | ANALYSIS OPTIONS                       | 05           |

| 2.7          | Sampled Voltage Analysis        |            | 7.1    | Model 4241 Define/Use                  | 20           |

| 2.8          | Positive/Negative Inputs        |            | 7.2    | Model 4242 Learn/Execute               | 32           |

| 2.9          | Sampled Voltage Analysis        | . /        | •      |                                        |              |

| 2.10         | Dead Time                       | . 7        | 8.     | WIRING OPTIONS                         |              |

|              |                                 |            | 8.1    | Model 4231A Mixer/Router Wiring        |              |

| 3.           | USING PHA and MCS               |            | 8.2    | Model 4232 External Control Wiring     | 34           |

| 3.1          | Setups                          | . 8        | 8.3    | Model 4233 Digital Stabilizer Wiring   | 36           |

| 3.2          | Data Acquisition                | . 8        | 8.4    | Model 4234 Pile-Up Rejection           |              |

| 3.3          | Data Manipulation               | . 9        |        | Live Time Correction Wiring            | 36           |

| 3.4          | MCS Mode                        | . 10       | _      |                                        |              |

|              |                                 |            | 9.     | SIGNAL PROCESSING OPTIONS              |              |

| 4.           | FRONT PANEL FUNCTIONS           |            | 9.1    | Model 4221 Amplifier/ADC               | 37           |

| 4.1          | Vertical Range and X2 Gain      | . 11       | 9.2    | Model 4222 High-Performance MCS        | 37           |

| 4.2          | Mixer/Router                    | . 12       | 9.3    | Model 4223 Multi-ADC Interface         | 37           |

| 4.3          | Memory                          |            |        |                                        |              |

| 4.4          | ADC Gain                        |            |        | ENDIX A.                               |              |

| 4.5          | ADC Offset                      | . 12       | Intern | nal Controls and Connector Signals     |              |

| 4.6          | Zero                            | . 12       | A.1    | Operating Voltage Selection            | 39           |

| 4.7          | Add and Subtract                | . 12       | A.2    | CPU Board                              |              |

| 4.8          | PHA                             |            | A.3    | ADC Board                              | 40           |

| 4.9          | MCSS                            | . 13       | A.4    | Display Board and Monitor              | 40           |

| 4.10         | MCSR                            | . 13       | A.5    | Miscellaneous Logic Board              | 40           |

| 4.11         | LLD (Lower Level Discriminator) | . 13       | A.6    | Low Voltage Power Supply               | 42           |

| 4.12         | ULD (Upper Level Discriminator) | . 13       | A.7    | X-Y Plotter Board                      |              |

| 4.13         | Amplifier Gain                  |            | 8.A    | Serial Interface Board                 | 43           |

| 4.14         | Clear Time and Clear Data       |            | A.9    | Mag Tape Interface Board               | 43           |

| 4.15         | Read In and Read Out            | . 13       | A.10   | GPIB Interface Board                   |              |

| 4.16         | Collect                         |            | A.11   | Rear Panel Connectors                  | 44           |

|              |                                 |            |        |                                        |              |

| 5.           | KEYBOARD FUNCTIONS              |            | APPE   | NDIX B.                                |              |

| 5.1          | Keypad                          | . 14       | Field  | Installation Instructions              |              |

| 5.2          | Control                         | . 14       | B.1    | Introduction                           |              |

| 5.3          | Overlap                         | . 14       | B.2    | Model 4222 High-Performance MCS Option | 54           |

| 5.4          | Transfer                        | . 15       | B.3    | Model 4223 Multi-ADC Interface         | 54           |

| 5.5          | Preset                          |            | B.4    | Model 4231A Mixer/Router Wiring        | 55           |

| 5.6          | Region of Interest              |            | B.5    | Model 4232 External Control Wiring     |              |

| 5.7          | Expand Mode                     | . 16       | B.6    | Model 4233 Digital Stabilizer Wiring   |              |

| 5.8          | Roll                            |            | B.7    | Model 4234 PUR/LTC Wiring              |              |

| 5.9          | Integral                        |            | B.8    | Models 4241 Define Use/AP-PAK and      | ٠.           |

| 5.10         | Cursor Control                  |            |        | 4242 Learn/Execute Options             | 57           |

| 5.11         | Index                           |            |        | odel 4251 X-Y Plotter Interface        |              |

| 5.12         | Home                            |            | B.10   | Model 4252 Printer Plotter Interface   |              |

|              | Energy Calibrate                |            | B.10   | 4253 Graphics Plotter Interface        |              |

| 5.13<br>5.14 | Ctrin                           | . 17<br>1Ω | B.12   | Model 4254 Magnetic Tape Interface     |              |

| 5.14         | Strip                           | , 10<br>10 |        |                                        |              |

| 5.15         | Spectrum Normalization          |            | B.13   | Model 4271 Computer Interface          |              |

| 5.16         | Ratio Computation               |            | B.14   | Model 4272 GPIB Interface              | ಯ            |

| 5.17         | Area                            | . 19       | B.15   | Models 4273, 4273A, 4273B              | 64           |

|              |                                 |            |        | LOMOUTER INTERTACES                    | n/4          |

|                           | Pa                                                                          | ge         |                                                                    | Pa                                                                                                                             | ae             |             |

|---------------------------|-----------------------------------------------------------------------------|------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|

| APPEND                    | DIX C                                                                       |            |                                                                    | · ¬                                                                                                                            | 3-             |             |

| ADC Zer<br>C.1 E<br>C.2 L | ro Adjustment Methods nergy Calibrate Method ive Source Method ulser Method | 65         | Figure 5-1<br>Figure 5-2<br>Figure 5-3<br>Figure 5-4<br>Figure 5-5 | Keyboard Layout Initial Energy Calibrate Lower Energy Peak Entered High Energy Peak Entered First ROI's Limits as Energy Units | 17<br>17<br>17 |             |

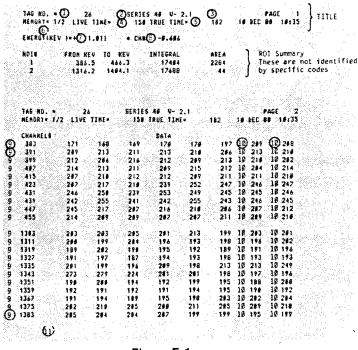

| APPEND                    |                                                                             |            | Figure 6-1<br>Figure 6-2<br>Figure 6-3                             | Full Memory Readout                                                                                                            | 21             |             |

| D.1 C                     | ational Methods<br>omputations                                              | <b>6</b> 6 | Figure 6-4<br>Figure 6-5                                           | Typical Graphics Plot                                                                                                          | 22             | <b>(</b> // |

| APPEND                    | IX E.<br>Itput Formats                                                      |            | Figure 7-1<br>Figure 7-2<br>Figure 7-3                             | Define Enabled                                                                                                                 | 28             |             |

| E.1 S                     | eries 40 ASCII Mode of I/Oeries 40 Binary Mode of I/O                       | 66<br>67   | Figure 7-4<br>Figure 7-5<br>Figure 7-6                             | Yes Reveals the X Register % ERR Equation Entered in X Register                                                                | 29<br>29<br>29 |             |

| APPEND                    | IX F.                                                                       | <b>.</b>   | Figure 7-7<br>Figure 7-8<br>Figure 7-9                             | Dialogue for Entering Constants  Variable Dialogue                                                                             | 29<br>29       |             |

|                           | Equations  kamples                                                          | 67         | Figure 7-10<br>Figure 7-11<br>Figure 7-12                          | Save Dialogue                                                                                                                  | 29<br>30<br>30 |             |

| APPEND                    | IX G.<br>/Option Compatibility                                              |            | Figure 7-13<br>Figure 7-14                                         | Variable 2 Entered as Counts Equation 2 Completed. USE Enabled                                                                 | 30<br>30<br>30 |             |

|                           | ptions and Successive Versions                                              | <b>6</b> 8 | Figure 7-15<br>Figure 7-16<br>Figure 8-1                           | Further Data Acquired                                                                                                          | 30<br>31<br>34 |             |

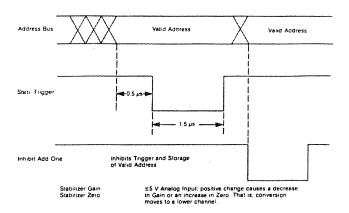

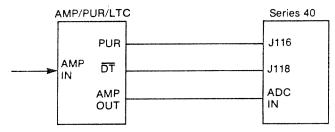

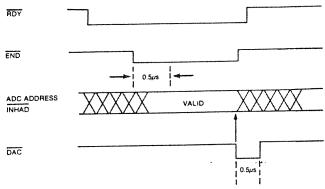

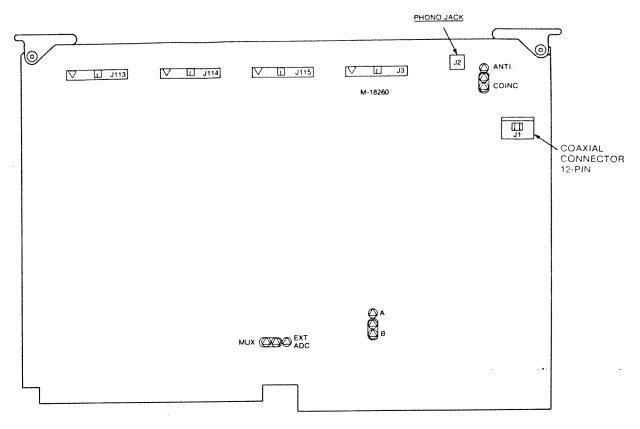

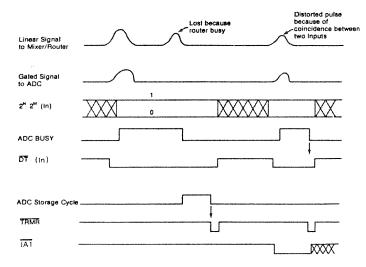

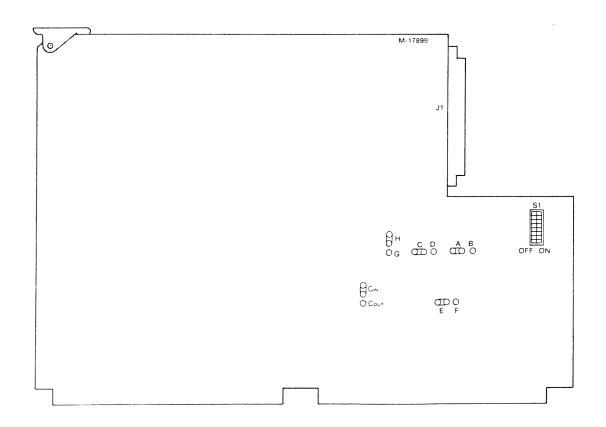

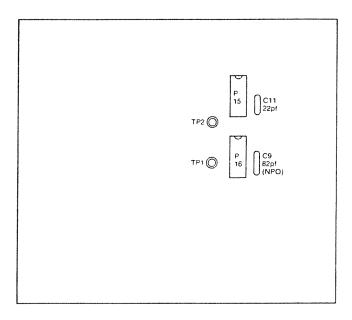

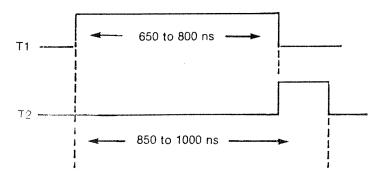

| GLOSSA                    | RY OF TERMS                                                                 | 70         | Figure 8-3<br>Figure 8-4<br>Figure 9-1<br>Figure 9-2               | System Interconnection PHA Cycle Timing Diagram                                                                                | 36<br>36<br>38 |             |

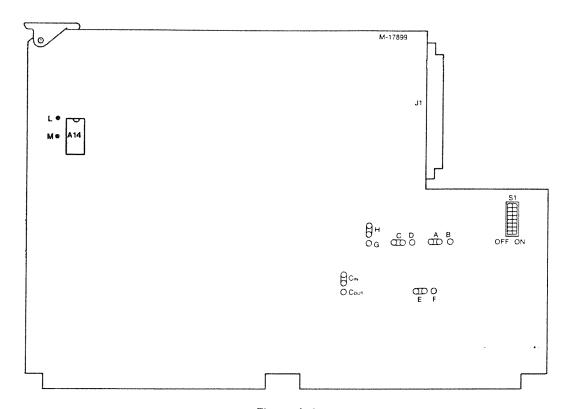

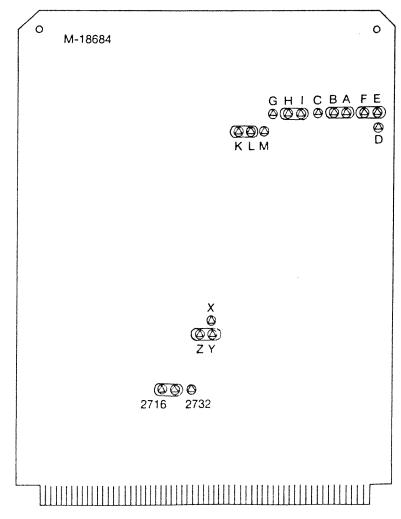

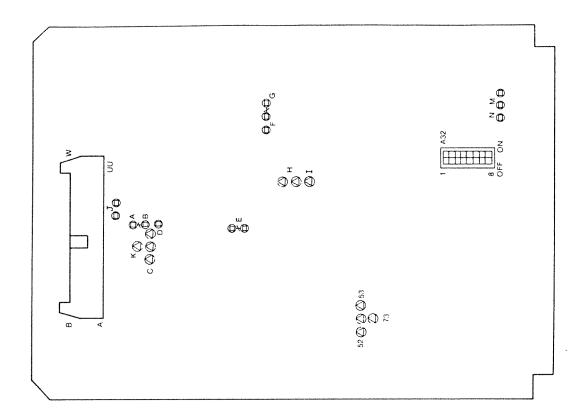

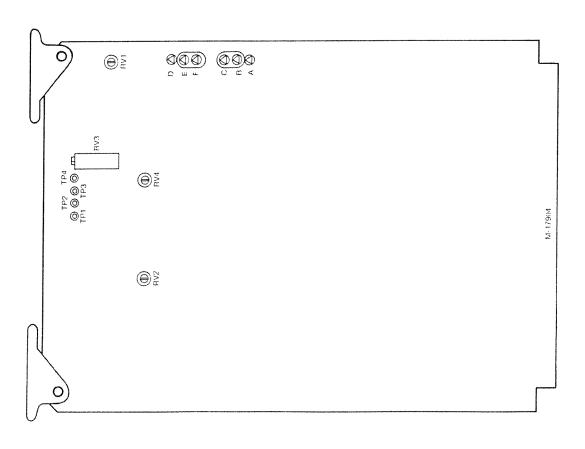

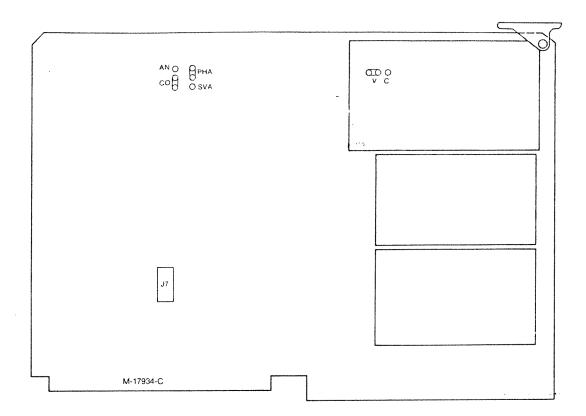

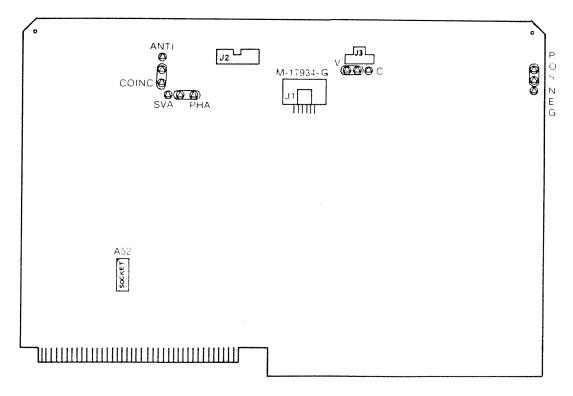

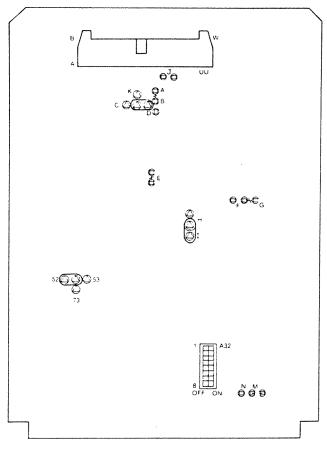

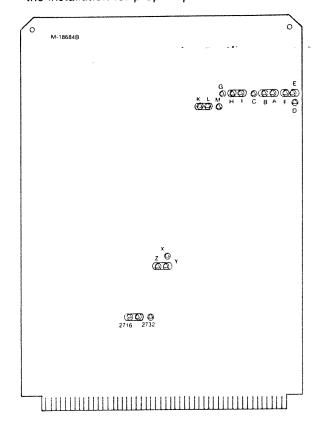

| *                         | FIGURE LISTING                                                              |            | Figure A-1<br>Figure A-2                                           | J4. Line Voltage Selection Card                                                                                                | 39<br>40<br>41 |             |

|                           |                                                                             |            | Figure A-3a<br>Figure A-3b                                         | Early ADC Board                                                                                                                | 41<br>41       |             |

| Figure 1-1                | Series 40 Block Diagram                                                     | 1          | Figure A-4                                                         | Miscellaneous Logic Board                                                                                                      | 42             |             |

| Figure 1-2                | PHA Operation                                                               | 2          | Figure A-4                                                         | Miscellaneous Logic Board                                                                                                      | 42             |             |

| Figure 1-2a               | Input Voltage Pulses                                                        | 2          | Figure A-5                                                         | Mag Tape Interface Board                                                                                                       | 44             |             |

| Figure 1-2b<br>Figure 1-3 | PHA Histogram                                                               | 2          | Figure A-6                                                         | X-Y Plotter Interface Board                                                                                                    | 45             |             |

| Figure 1-3a               | Pulse Train Conversion to a PHA Histogram                                   | 3          | Figure A-7                                                         | Serial Interface Board4                                                                                                        | 45             |             |

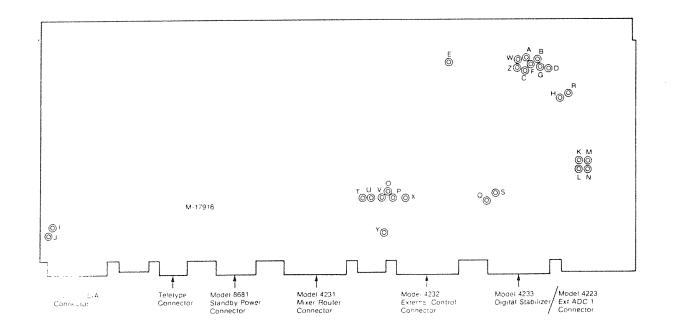

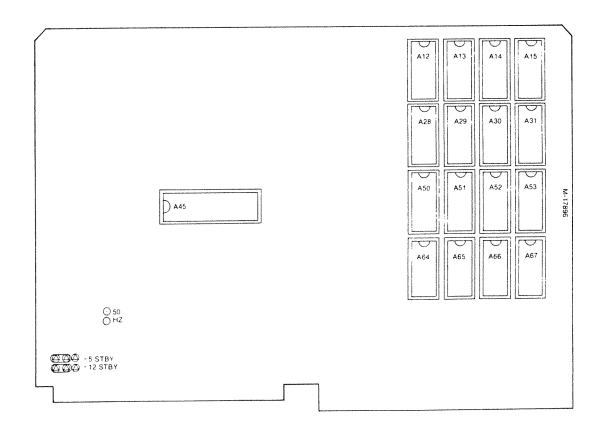

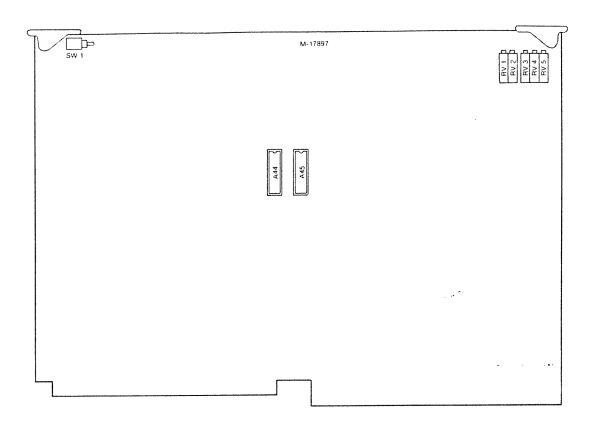

| Figure 1-3b               | Voltage Train Output from NaI Detector                                      | 3          | Figure A-8                                                         | Series 40 Rear Panel                                                                                                           | 16             |             |

| Figure 1-4                | Effect of 8192 Conversion Gain and 4096                                     | 3          | Figure B-1                                                         |                                                                                                                                | 50             |             |

| ga.c                      | Channel Memory                                                              | 3          | Figure B-2                                                         | Series 40 Rear Panel                                                                                                           | 51             |             |

| Figure 1-5                | Multichannel Scaling                                                        | 4          | Figure B-3                                                         | Mother Board - Bottom View                                                                                                     | 51             |             |

| Figure 1-5a               | Input Pulse Train                                                           | 4          | Figure B-4<br>Figure B-5                                           | CPU Board                                                                                                                      |                |             |

| Figure 1-5b               | MCS Histogram                                                               | 4          | Figure B-6                                                         | District D                                                                                                                     | 3              |             |

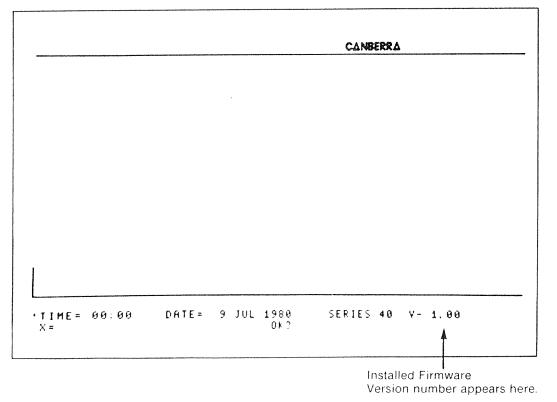

| Figure 2-1                | Initial Display                                                             | 5          | Figure B-7                                                         |                                                                                                                                | 3              |             |

| Figure 2-2                | Signal Connectors                                                           | 6          | Figure B-8                                                         |                                                                                                                                | 34             |             |

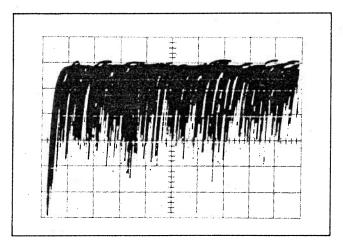

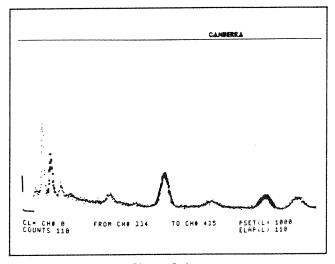

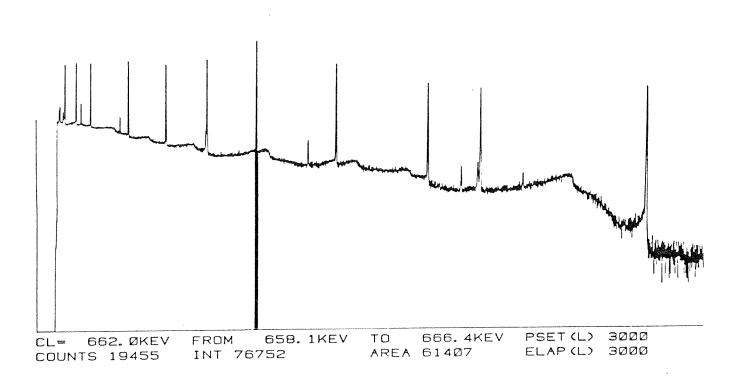

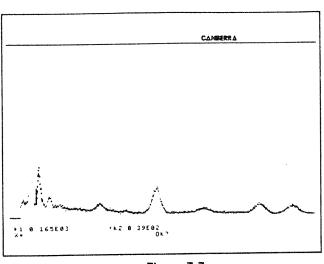

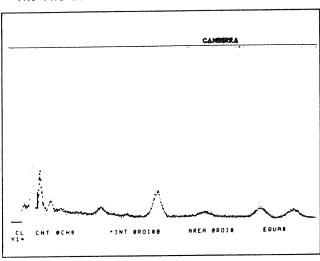

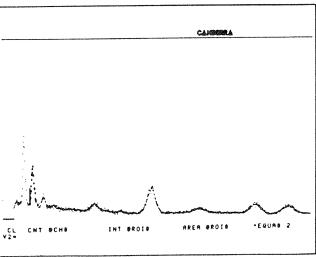

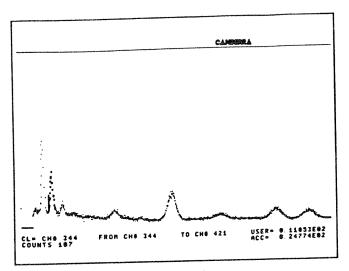

| Figure 2-3                | Typical PHA Spectrum (Nal detector) showing Dead Time Bar Graph             | 7          | Figure B-9<br>Figure B-10a                                         | Model 8200-PC1                                                                                                                 | 54<br>56<br>58 |             |

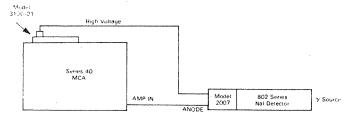

| Figure 3-1                | Charge Sensitive System Setup                                               | 8          | Figure 8-10b                                                       | Revision G ADC Board 5                                                                                                         | 8              |             |

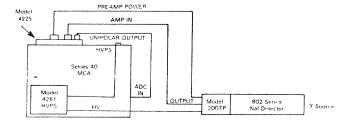

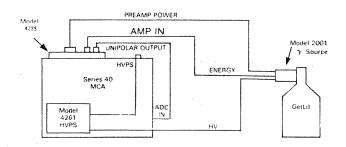

| Figure 3-2a               | Voltage Sensitive System Setup (Nal)                                        | 8          | Figure B-11                                                        | Model 4252 Printer/Plotter Interface Board                                                                                     | 0              |             |

| Figure 3-2b<br>Figure 3-3 | Voltage Sensitive System Setup [Ge(Li)]                                     |            | Figure B-12                                                        | Magnetic Tape Interface Board 6                                                                                                | 1              |             |

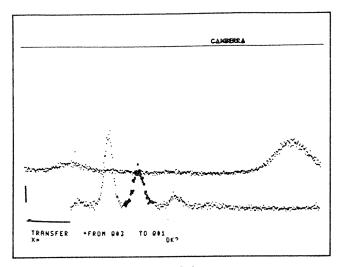

|                           | Transfer Dialogue and Display                                               | 9          | Figure B-13                                                        | Model 4271 Computer Interface Board 6                                                                                          | 4              |             |

| Figure 3-4<br>Figure 3-5  | Nal Spectrum with 3 ROI's Entered                                           | 9          | Figure B-14                                                        | Model 4272 GPIB Interface Board                                                                                                |                |             |

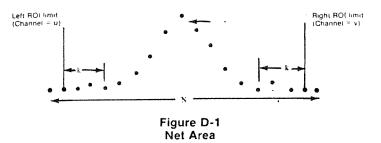

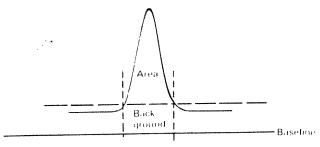

| Figure 3-5                | An Expanded ROI                                                             | 9          | Figure D-1                                                         | Net Area                                                                                                                       | 6              |             |

| Figure 3-6                | An ROI with AREA Enabled                                                    | 9          | Figure E-1                                                         | Sample ROI Readout from                                                                                                        |                |             |

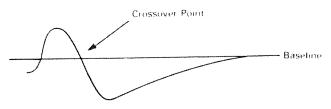

| Figure 3-8                | Strip Dialogue and Display                                                  |            |                                                                    | Series 40 ASCII Mode                                                                                                           | 7              |             |

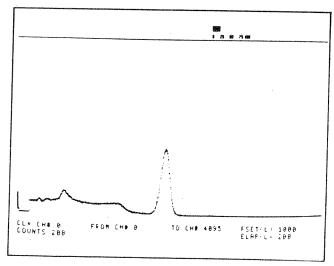

| Figure 3-9                | has Zero Counts Typical MCSR Spectrum after 187 251 Sweeps                  | 11         | 1                                                                  |                                                                                                                                |                |             |

| Figure 3-10               | X2 Enabled                                                                  | 11         |                                                                    |                                                                                                                                |                |             |

| Figure 4-1                | Front Panel                                                                 | 11         |                                                                    |                                                                                                                                |                |             |

### PREFACE

The Series 40 Operator's Manual is organized so that it can be used by both the experienced MCA operator and the newcomer to nuclear analysis. It is divided into several sections for ease of reference:

- An introduction to the Series 40 Multichannel Analyzer and a basic description of the two modes of operation—PHA and MCS.

- 2. Basic operating rules for the Series 40.

- 3. Two simple experiments to show how to use the PHA mode and the MCS mode.

- 4. A description of the Front Panel functions.

- 5. A description of the Keyboard functions.

- 6. A section dealing with the input and output of data.

- 7. A section covering the Analysis Options.

- 8. A section on the Wiring Options.

- A section concerning the Signal Processing Options.

The experienced MCA operator may wish to proceed directly to sections 2, 4, and 5 to learn the specific functions of the Series 40 MCA. The less experienced operator should study the first sections before attempting more than the most basic use of the analyzer. Sections 4 through 8 assume a working knowledge of sections 1,2 and 3.

#### CLEANING THE FAN FILTER

The fan filter at the rear of the Series 40 must be cleaned periodically (every month or so, depending on the

environment) to assure a flow of cooling air to the interior of the analyzer.

If the internal temperature of the Series 40 analyzer is allowed to rise above a safe level, a thermal cutout will remove power from the analyzer to allow the temperature to go down. This will, of course, cause data to be lost unless the Model 8681 Standby Power Supply is connected to the analyzer.

To clean the filter, pull it out of the fan mount. After thoroughly cleaning the filter, replace it inside the fan mount so that the filter completely covers the fan's air intake opening.

The filter may be cleaned by brushing, by blowing with compressed air or by washing. If the filter is washed, be certain that it is completely dry before replacing it in the analyzer.

#### **CLEANING THE MONITOR**

A high-voltage induced static charge on the face of the display monitor can attract dust. To remove the dust, clean the face of the monitor with a soft cloth dampened with water. Note that the area being cleaned is a plastic anti-glare filter; take care not to scratch it.

To avoid further static charge accumulation while wiping the screen, hold on to the frame of the Series 40 while cleaning the display.

## Section 1. Introduction

1.1 General Description

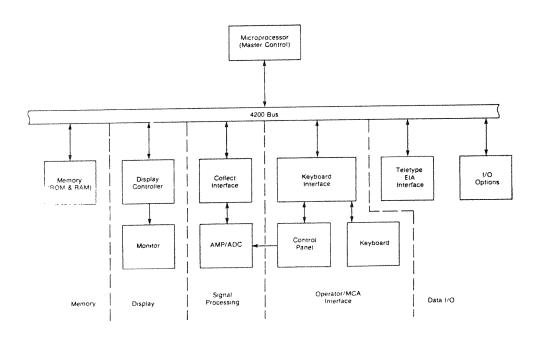

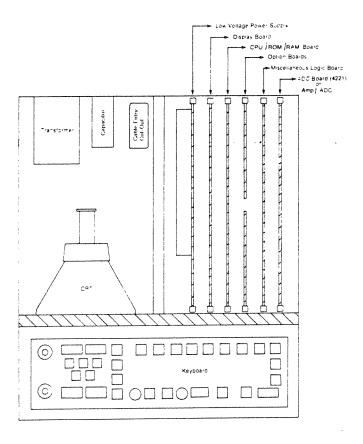

Functionally, the Series 40 consists of a master controller and five sections: memory, display, signal processing, operator/MCA interface, and data input/output. The controller is a microprocessor which reads its instructions from a permanent program in the memory which controls the MCA functions and directs the use of the 4200 bus. See Figure 1-1.

The memory consists of the preprogrammed Read Only Memory (ROM), which contains the instructions for the microprocessor (firmware), and the Random Access Memory (RAM), which stores operator instruction and the acquired data.

The Series 40 is offered with data memory of 1024, 4096 or 8192 channels. Memory storage in RAM can take place in the full memory, either half of the memory or any quarter of the memory as selected by the operator. Data storage may be either in the Pulse Height Analysis (PHA) mode, the Sampled Voltage Analysis (SVA) mode, or the Multichannel Scaling (MCS) mode. For both PHA and MCS, the data may be added to or subtracted from the memory.

The display section of the Series 40 directs the data in the memory to the large screen display and organizes it in a readily understood format. The operator is supplied with a clear picture of the spectral data in memory and with appropriate information in alphanumeric form as an aid in interpreting the data displayed.

The signal processing section includes a preamplifier/amplifier that may be configured by the

operator to accept either charge-sensitive input signals or voltage-sensitive input signals, depending on the type of detector to be used. The signals are passed to an Analog-to-Digital Converter (ADC), which converts the input linear signals to digital form and routes them to the appropriate memory location for storage and subsequent display, analysis and readout.

The operator/MCA interface allows the operator to direct the tasks of the MCA by means of the settings of the control switches on the Control Panel and the pushbuttons on both the Control Panel and the Keyboard. The operator's instructions are routed through the keyboard interface to the RAM section of the memory by way of the microprocessor and the 4200 bus.

The input/output (I/O) section controls the data flow between the RAM section of the memory and the various peripheral devices. As a standard feature, this section includes the I/O interfacing needed to handle current-loop (Teletype) and either EIA RS232 devices or the Canberra Model 5411 Digital Cassette Recorder.

Provision is made for the operator to read prerecorded data into the memory as well as reading data out of the memory in the operator's choice of: full, half or quarter memory; any Regions of Interest, as specified by the operator.

By dividing the MCA's full range of operating features and analysis functions between several sections controlled by a high-speed microprocessor, the Series 40 has been made into an instrument that is well suited to both basic and advanced nuclear analysis needs.

Figure 1-1 Series 40 Block Diagram

#### 1.2 Applications

From a data acquisition point of view, all Series 40 Multichannel Analyzer applications can be placed into one of two categories: Pulse Height Analysis (PHA) or Multichannel Scaling (MCS). These two analysis modes and their applications are discussed in the following sections.

#### 1.2.1 Pulse Height Analysis

In the PHA operating mode, a train of pulses, such as those from a radiation detector, are applied to the input of the Series 40. These pulses have amplitudes (heights) which are proportional to the energies of the incident radiation that was absorbed by the detector. By counting the number of occurrences of pulses of each height and forming a histogram, the Series 40 records the radiation energy spectrum as seen by the detector.

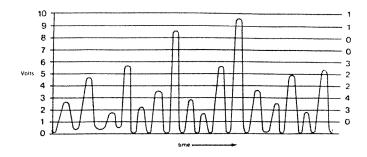

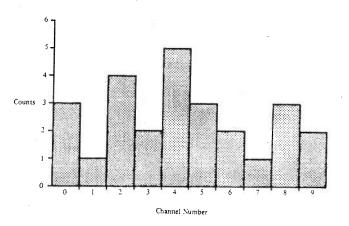

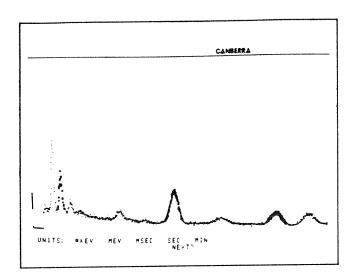

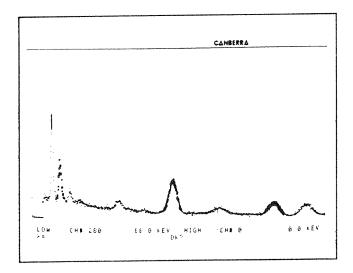

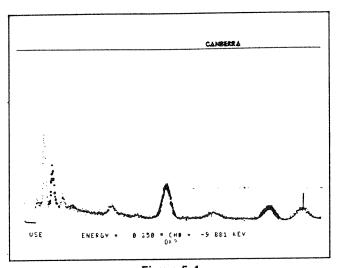

A better term for Pulse Height Analysis would be Pulse Height Distribution Analysis, because the input pulses are sorted by voltage amplitude to yield a histogram representing frequency of occurrence versus pulse height. A pictorial representation of this process can be seen in Figure 1-2.

Figure 1-2a depicts a series of voltage pulses as they might appear at the input to the Series 40. The vertical axis has been divided into ten (10) equally spaced intervals, each representing one volt of pulse height. At the right of the figure the number of pulses falling into each of the various intervals is tabulated. This same data is then shown in histogram form in Figure 1-2b, where the horizontal axis divisions correspond to the voltage divisions on the original signal. It is this type of pulse height distribution analysis that is performed by the Series 40 MCA during PHA mode data acquisition.

The primary application of PHA operation is in the quantification of the output signals from the class of radiation detectors whose output is a current or voltage pulse proportional in amplitude to the energy absorbed by the detector. Typical of such detectors are Scintillation detectors such as NaI(TI), Semiconductor detectors such as Ge(Li), HPGe, or Si(Li) and Gas Proportional detectors.

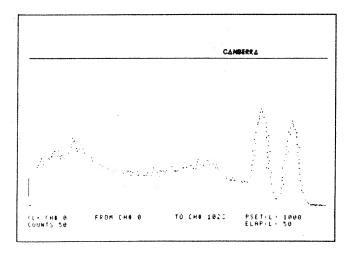

A common characteristic of all these detectors is that each current or voltage pulse produced by the detector corresponds to the energy deposited by an individual photon or particle. Since the nuclear or atomic decay which generates the incident radiation is a randomly occurring process, the pulse train from the detector to the Series 40 is a time-random mixture of pulses of all possible amplitudes. The job of the Series 40, in PHA operation, is to sort this pulse train by amplitude and store the resultant spectrum. This can be seen graphically in Figure 1-3, where both the detector output and PHA histogram for a Cobalt-60 source are shown.

The 1024 channel histogram shown in Figure 1-3b is directly analogous to the ten channel histogram in Figure 1-2b but is of far greater resolution. That is, the input pulses have been sorted into 1024 discrete amplitude levels rather than just ten levels. Each point in the Figure 1-3b display represents the number of counts accumulated in one particular channel; it is still a pulse height distribution histogram.

#### a. Input Voltage Pulses

#### b. PHA Histogram

#### Figure 1-2 PHA Operation

From an analytical point of view, a PHA distribution histogram (spectrum) can provide both qualitative and quantitative results. Since channel number corresponds to input voltage, and input voltage corresponds to the energy of the radiation striking the detector, the energy of any peak in the spectrum can be easily determined; and from the energy (or energies) present one can determine the source.

The spectrum can also yield quantitative data. Since all measurements of radiation intensity are based upon the number of events per unit time, one need only divide the number of occurrences of a given energy by the total acquisition time to get a measure of the activity present. This is, of course, an oversimplification, since there are many other physics-related factors that must also be considered. But conceptually, the principle of "counts divided by time" is valid.

Because of this, when operating in PHA mode, the Series 40 stores acquisition time along with the spectral data. Channels 0 and 1 of the Series 40's memory are reserved for the time storage function. Channel 1 stores true (real) time.

The time value stored in channel 0 is generated by a special circuit called a "live time clock", and the value accumulated is called the "live time". The need for this special time circuit can be seen by examining in closer detail the operation of the Series 40 PHA in relation to the input pulse train.

From a time standpoint, the input pulse train is totally random in nature. Therefore, since it does take the analog-to-digital converter (ADC) a finite amount of time to convert a pulse amplitude into a channel number, some

pulses will arrive at the ADC only to discover that it is busy processing the previous pulse. The ADC is effectively "dead" and this datum (pulse) is lost.

Because of this "dead-time" phenomenon, a time correction circuit is required to compensate for the fact that the number of input pulses per unit time can vary considerably from the number of events stored per unit time. This time correction circuit, called the "live time clock", extends the total elapsed counting time to compensate for the percentage of time that the ADC is "busy". This circuitry can be seen in operation via the % Dead Time bar-graph at the top of the Series 40's display.

For PHA operation, the primary goals are, therefore, the ability to measure the distribution of input pulse heights and to keep track of the system live counting time. The time function is automatically handled via the live time clock and requires no parametric input. However, the Series 40 does provide several methods for modifying the parameters of the pulse height distribution function.

#### a. Voltage Train Output from Nal Detector

#### b. Resultant Series 40 PHA Histogram

Figure 1-3

Pulse Train Conversion to a PHA Histogram

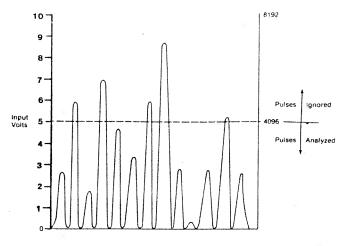

Figure 1-4

Effect of 8192 Conversion Gain and 4096 Channel Memory

#### 1.2.1.1 ADC Gain

One of the factors affecting the generation of a pulse height distribution histogram is the system resolution; that is, the number of discrete voltage levels - or channels - into which the input pulses will be sorted. In ADC terminology, this is called the ADC Conversion Gain. For example, our initial histogram (in Figure 1) used ten separate one-volt levels for sorting; it had an ADC Gain of 10.

For most PHA operations, the intent is to analyze the input voltage over its entire 0 to 10 volt range. To do this with maximum resolution, the ADC Gain is set equal to the Memory Size. This corresponds to an ADC Gain of 4096 channels on the Series 40 (Model 4202).

Alternatively, an ADC Gain of 2048 channels would allow two separate spectra to be stored in either half of the 4096 channel memory.

#### 1.2.1.2 Digital Offset

For situations requiring greater resolution, the Series 40 ADC provides an ADC Gain of up to 8192 channels. However, since the Model 4202 memory provides only 4096 channels of storage, only a portion of the input voltage range can be examined at one time using the 8192 channel ADC resolution.

If one were interested only in the first five volts of the zero to ten volt input range, the experiment setup would be quite straightforward, as shown in Figure 1-4. Pulses below the five volt (channel 4096) level are analyzed and stored; those above are ignored.

But what if the objective is to analyze those pulses in the five to ten volt range: how can this be accomplished? It is in this situation where the value of ADC Offset can be seen.

Up to this point, it has been assumed that ADC channel numbers and memory channel numbers are the same. In reality they are independent; and it is the ADC Offset control which establishes their relationship.

When the ADC and memory channel numbers are the same, the ADC Offset is said to be zero. This relationship can be shifted linearly via the ADC Offset control. For example, to analyze the upper five to ten volt range of the input using a 8192 channel ADC Gain and a 4096 channel memory, what is needed is to "shift" the zero channel of the memory to correspond to channel 4096 of the ADC. In other words, an ADC Offset of 4096 channels is required. The Series 40 includes 32 different ADC Offset settings to allow the selection of the optimum value for any given situation.

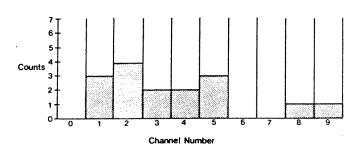

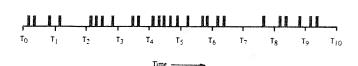

1.2.2 Multichannel Scaling

MCS analysis yields a histogram representing number of events (radiation intensity) versus time. Just as in PHA, the input signal is a train of pulses, each representing a single event. However, MCS analysis does not concern itself with the amplitude of these pulses; the data stored is simply the number of individual pulses which were received in a given period of time.

As pulses are detected at the input of the Series 40, MCS mode operation counts them one-by-one into the current memory channel for a predetermined period of time. At the end of this time period, which is called the dwell time, the MCS time base advances to the next memory channel address. Pulses are now counted into this channel for the dwell time period. Each memory channel is thus sequentially selected as a function of time.

This operation can be seen in a simplified form in Figure 1-5. The input pulse train in 1-5a would generate the histogram shown in 1-5b. Note that an MCS analysis produces an integral histogram; each channel represents the summation of all counts within the given time period and not the instantaneous count rate.

MCS analysis finds use in several applications involving the study of the distribution of events as a function of time. One such application is the study of nuclear decay; the resultant MCS histogram represents the exponential decay curve.

Many other applications - such as Mossbauer spectrometry - involve the synchronization of the MCS scan to an external device. In this case, the time axis really relates to an external device position or condition, such as source velocity in the case of Mossbauer work.

For all applications an appropriate dwell time must be selected prior to the analysis. Several factors can influence this choice.

- I. Desired time for the entire scan.

- 2. Number of channels to be used for data storage.

- Desired counting statistics (number of counts per channel).

- 4. Operating rate of an external device.

In many cases, several of these criteria may be incompatible. For example, the sweep rate of a Mossbauer spectrometer may be too rapid to allow collection of adequate statistics in a single data acquisition scan. For these situations the Series 40 provides an MCSR operating mode, which allows recurring, or multiple, MCS acquisition sweeps.

Depending upon the external device being used, it may be necessary to synchronize these recurring sweeps to the mechanical motion. The Model 4232 External Control Wiring option provides this capability.

a. Input Pulse Train

b. MCS Histogram

# Section 2. Basic Series 40 Operation

#### 2.1 Power On

This section describes the operation of the Series 40 Multichannel Analyzer and the basic dialogue rules

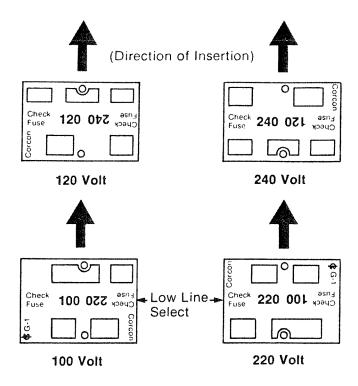

Power is applied to the Series 40 with the ac power switch on the analyzer's rear panel. Before applying power, check the voltage selection card inside the fuse compartment on the rear panel. This is easily done by moving the plastic fuse shield to the left and looking directly under the fuse; the operating voltage will be visible. Should it be necessary to change the operating voltage, refer to Appendix A.1 for instructions.

The analyzer will be set for either 50 Hz or 60 Hz operation. If it should be necessary to change line frequency, refer to Appendix A.2 for instructions.

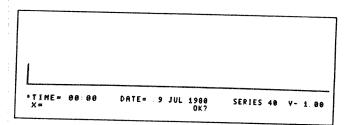

The intensity of the display is controlled by the INTENSITY potentiometer located on the left side of the Keyboard. A few seconds after power on, the display will appear and will look as shown in Figure 2-1. This System Initialization state shows the internal clock time starting at 00:00 and the date on which the installed firmware was released to production.

Note that the LED indicators for PHA and ADD on the Control Panel are illuminated. The analyzer's default state assumes that the most common operating mode will be used; changing these modes is done by pressing a pushbutton for another mode. See Section 4 for examples.

Figure 2-1 Initial Display

The usual first step after power is applied is the setting of the clock and the calendar to current values. If new values are not entered, the clock and calendar will keep time from 00:00 of the firmware release date.

The procedure for entering new values is as follows:

- Using the numeric keypad on the right side of the Keyboard, enter the correct time in the form Hours.Minutes on a 24 hour basis. Note that the value if first entered in the X Register.

- 2. If an error is made in the entry, the red CLEAR key on the keypad can be used to erase the value of X. A new value may then be entered in the X Register.

- Press STORE on the keypad to transfer the entry from the X Register to the TIME variable.

- 4. Press NO to move the \* to DATE and enter the new value for the date in the form DD.MM.YY and press STORE. Note: The year must be entered using the year's last two digits only. That is, 1981 is entered as 81.

- Press YES (in answer to the question OK?) to have the new values accepted and the system revert to a normal display (Figure 2-2).

### 2.2 System Initialization

Associated with the Expand and Integrate functions is the Power Reset command. It is activated by simultaneously pressing these two pushbuttons. Issuing a Power Reset command aborts any operation in progress but does not alter any time or data information nor does it alter any operator-set parameters. Power Reset does not normally need to be used to abort an operation because all operations can be terminated simply by turning the function off.

Performing a Power Reset causes the display to revert to the initial power-on display seen in Figure 2-1 and thus can be used to check the status of the system time and date clock and the Firmware version. Answering YES to the question OK? will return the system to the normal display.

Note that the Power Reset has returned the system to the initial PHA/ADD state from any other data acquisition mode previously selected.

### 2.3 Basic Dialogue Procedures

The brief process of entering the current time of year, described in the previous section, illustrates many of the basic dialogue "rules" common to all Series 40 operations. As the remainder of the manual is read, many additional examples will be seen. The following is a summary of those rules which are, in general, applicable to any dialogue sequence.

- If a dialogue sequence is capable of accepting a numeric parameter, the X Register (X= ) will be displayed on the lower left portion of the CRT.

- During the entry of a numeric parameter, it is displayed as it is typed in the X Register. Errors may be corrected by touching CLEAR and re-entering the value.

- Touching STORE causes the entry in X to be evaluated and transferred to the parameter field being modified.

- 4. A numeric entry, up to 16 displayed characters, can be entered as an arithmetic operation. For instance, 5120 can be entered as X = 4096 + 1024. This entry will be evaluated and stored as 5120 when the STORE key is pressed.

- The parameter field currently selected for modification is the one adjacent to the blinking \*. To select a different parameter for modification, the

blinking \* must be moved to the desired parameter field.

- When several choices are listd on a line, touching NO moves the blinking \* to the next parameter in sequence on the line.

- 7. When the question NEXT? is displayed, touching YES will mean "what is displayed is acceptable; go on to the next step." When the question OK? appears, YES will mean "I agree; end the dialogue."

- 8. If a dialogue procedure is aborted (by turning off the function rather than answering all questions), all original values are maintained as if the function was never started.

- An illegal entry will generate an error message. To proceed, touch CLEAR on the numeric keypad and re-enter the correct value.

- 10. Under some conditions, a numeric display may show either a series of asterisks (\*\*) or, in later Firmware versions, a series of "greater than" signs (>>). This indicates that the number is too large for the display area; the number will be correctly stored in memory.

The Series 40 also offers an additional operating characteristic that most users will find very beneficial after some "hands on" experience is gained: Console Function Typeahead. That is, as buttons are pushed, the code for each is stored in list (on a First In, First Out basis) and then retrieved in sequence for execution. This allows an operator who is familiar with a procedure to quickly touch all needed buttons, in the correct sequence, without waiting for the displayed dislogue to "catch up".

#### 2.4 LED INDICATORS

Most of the pushbuttons have a built-in light-emitting diode (LED) indicator to show the status of the associated function. The few pushbuttons lacking an indicator are "momentary" functions; that is, the function does not remain enabled after the pushbutton is released.

When any pushbutton with an indicator is pressed, the function is enabled, and the LED is illuminated to show the status of the function. Pressing the pushbutton a second time will disable the function, turn off the indicator, and abort any process that was initiated when the function was enabled.

Note that any prerequisites must be fulfilled before some of the functions can be enabled. For example, OVLAP cannot be enabled usless the MEMORY switch is in a position other than 1/1.

#### 2.5 SIGNAL CONNECTORS

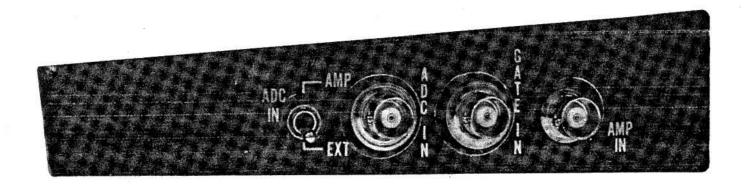

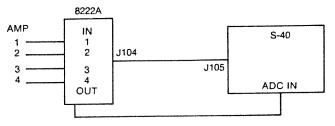

Figure 2-2 illustrates the three BNC type signal connectors. Two of these, labled ADC IN and AMP IN, are analog signal inputs. The other connector, labeled GATE IN, accepts logic signals to condition the ADC to either accept or reject analog signals for conversion. See Section 2.6, following, for information concerning use of the GATE input.

The AMPlifier INput can route signals from an external preamplifier to the internal amplifier or from a detector to the internal preamplifier. The ADC INput accepts 0 to 10V signals from an external amplifier which can then be processed by the ADC.

The adjacent ADC IN switch must be in the correct position for the input connector used. The AMPlifier position allows signals from the internal amplifier to be routed to the ADC; the EXTernal position connects the ADC INput connector directly to the ADC, bypassing the internal amplifier.

Figure 2-2 Signal Connectors

Care should be taken to keep the signal cables away from the CRT because it is possible for the CRT to induce noise on these input lines.

The rear panel has a number of other connectors. Their uses will be covered in Sections 7 and 8.

#### 2.6 GATE

The GATE function allows the operator to enable or disable the ADC for acceptance and conversion of linear signals at its input. Depending on the criteria for the experiment in progress, the operator may use the GATE input in the factory-set coincidence mode or may change the function to the anticoincidence mode by moving a jumper on the ADC board (see Appendix A.3).

The GATE input signal must be coincident in time with the linear signal in order to be considered by the ADC regardless of the mode chosen.

#### In the Coincidence mode:

- A low logic level (0 to 0.8 volts) at the GATE connector will disable the ADC. It will neither accept nor process any linear signals while the GATE is low.

- A high logic level (2.5 to 5.5 volts) at the GATE connector will enable the ADC. It will accept and convert all linear signals received while the GATE input is high.

- If the GATE input is left open (unconnected), the ADC will act as if the GATE Input is high and will accept and convert all linear signals received.

In the Anticoincidence mode, the logic is reversed. That is, a low logic level will enable the ADC and a high level (or an open input) will disable the ADC.

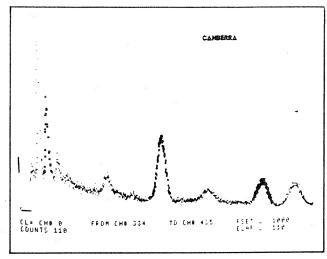

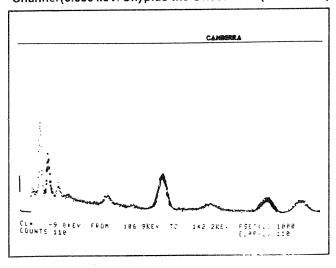

Figure 2-3

Typical PHA Spectrum (Nal detector)

showing Dead Time bar graph

2.7 INPUT

The Series an external

from the AM

The Analyzi detector, as moving a ju Moving the internal preamplifier.

2.8 POSITI In the Voltac factory-set f A.3 for ins negative-go

2.9 SAMPL In the Samp voltages (do sampled by distribution of signal and m ULD control

The GATE i must be coir

To use the ar jumper on the position. See PHA mode, position.

2.10 DEAD Any signal the the ADC is padd. This is previous significated with Dead Time.

The Dead Till moving bar COLLECT m

Note that any the factory se even though

# Section 3. Using PHA and MCS

This section will outline two possible experimental setups using the Series 40 and either a charge sensitive input (from a scintillation detector, such as Canberra's model 802 series) or a voltage sensitive input (from any other type of detector). See Appendix A.3 for instructions on changing from one type of input to the other. If a scintillation detector is connected to an external preamplifier the preamp's output can be connected to the Series 40 as a voltage sensitive input.

#### 3.1 SETUPS

For a charge sensitive input, the following equipment, or equivalent, will be required:

- · Series 40 MCA

- Model 3100-01 or Model 4261 High Voltage Power Supply (HVPS)

- · Model 802 series Scintillation Detector

- · Model 2007 Photomultiplier Tube Base

- · Cables for interconnection as shown in Figure 3-1.

Figure 3-1

Charge Sensitive System Setup

For a voltage sensitive input, the following equipment, or equivalent, will be required:

- · Series 40 MCA

- · Model 4261 High Voltage Power Supply (HVPS)

- Model 4225 Spectroscopy Amplifier; Nal detectors can use the internal amplifier.

- A Ge(Li) detector with a Model 2001 Preamplifier or a Model 802 Detector with a Model 2007P Preamplifier.

- · Cables for interconnection as shown in Figure 3-2.

Figure 3-2a

Voltage Sensitive System Setup (Nal)

Figure 3-2b

Voltage Sensitive System Setup [Ge (Li)]

#### 3.2 DATA ACQUISITION

Initial Control Panel Settings:

| ADC IN SWITCH | AMP (EXT IN for Figure 3-2a) |

|---------------|------------------------------|

| VERTICAL RANG | SE 1K or LOG                 |

| MEMORY        | 1/1                          |

| ADC GAIN      | 1024 for Model 4201          |

| ,             | 4096 (for Model 4202)        |

|               | 8192 (for Model 4203)        |

| ADC OFFSET    | None: all switches down      |

| SCA LLD       | 0.20                         |

| SCA ULD       | Fully clockwise (10)         |

| MODE          | PHA and ADD (default state). |

|               |                              |

- 1. Turn on the Series 40 with the ac power switch, set time and date if desired and press YES.

- 2. Turn on the HVPS with its separate switch.

- 3. Set the HVPS to the correct operating voltage for the detector being used.

- Place a radioactive source near the face of the detector.

- Press COLLECT to start data acquisition. Note that the LED indicator is illuminated in the COLLECT pushbutton, showing that acquisition is in progress. Note the Dead Time meter displayed at the top of the screen.

- 6. Adjust the AMPLIFIER GAIN so that the spectrum (data being displayed) is positioned conveniently on the display.

- Pressing CLEAR DATA repeatedly while adjusting the AMP GAIN will aid in positioning the spectrum.

- 8. Allow the data to accumulate for a few minutes.

- 9. Press COLLECT again to stop acquisition. Note that the LED indicator is no longer illuminated.

Figure 3-3

Transfer Dialogue and Display

Figure 3-4

Nal Spectrum with 3 ROI's Entered

#### 3.3 DATA MANIPULATION

To see the effects of some of the Keyboard functions:

- 1. Change the MEMORY switch to 1/4.

- Press XFER. Note that the dialogue asks if the operator wants to transfer Q # 3 to Q # 1 (memory quarter number three to memory quarter number one). The contents of Q # 3 are displayed above the contents of Q # 1.

- Press YES to enable the transfer. Note that the upper data trace is no longer displayed and the data has been copied into the memory section being viewed (Q # 1).

- 4. Press OVLAP. Note that the MCA displays the two quarters with the upper data offset by 20% above the lower data, as in step 2. The dialogue asks "Q#3 over Q#1 OK?". Pressing YES will terminate the overlap dialogue, but the overlapped data will still be displayed.

- Press OVLAP again to disable the function. Note that the display returns to normal; that is, the overlapped data is no longer displayed.

- At the bottom of the Keyboard is a double headed arrow. The two buttons within the arrow heads are

the cursor scan controls, which move the cursor to the right or to the left through the spectrum. Press the Scan right button and watch the cursor move slowly to the right and then gradually move faster. When the cursor is at the beginning of a peak in the spectrum, release the Scan button to stop cursor motion.

- Press ENT ROI and Scan the cursor to the right again. Note that the data points in the peak are intensified as the cursor moves through them.

- Release the Scan button and press ENT ROI once more to disable the function. A Region of Interest has now been entered around the peak. Repeat steps 7 and 8 for several more peaks.

- Press INDEX and watch the cursor jump from the beginning of one ROI to the beginning of each succeeding ROI in turn. Note that the cursor will index from the last ROI in the spectrum to the first ROI. This is what is meant by "around the corner" indexing.

- Press EXPAND to see the display change to include only 128 channels, with the cursor at the 25% point of the Expanded display.

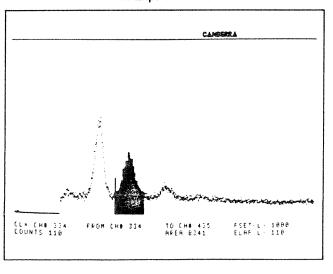

Figure 3-5 An Expanded ROI

Figure 3-6

An ROI with AREA Enabled

Figure 3-7

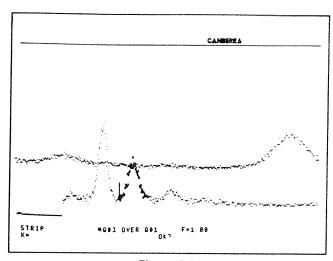

Strip Dialogue and Display

Figure 3-8 Clear Time Performed, Channel 0 has Zero Counts

- 11. Press ROLL and then scan the cursor to the right. Note that the cursor stays centered in the display and the data appears to move to the left as the 128channel window is scanned to the right through the spectrum.

- 12. Press EXPAND again to disable the function. Note that the ROLL function is disabled simultaneously.

- 13. Press INDEX to put the cursor in an ROI Press AREA and note that the ROI now has vertical histogram bars entered from the baseline to the data point in each channel in the ROI. The value of the area is shown at the bottom of the screen. Press ABEA again to disable the function.

Press INTEG to compute the integral value of the ROI. Make a note of the value as displayed at the bottom of the screen. Disable INTEG.

Press STRIP. Observe the flashing \* in the dialogue. Press NO to advance the \* to F 1.00.

- Change the value of the factor (F) by entering a decimal point, the numeral 5 and pressing STORE. F should equal 0.5.

- 18. Press YES to allow the Strip to proceed. The display will flash BUSY! at the bottom of the screen while the Strip is active to indicate that the analyzer is unable to perform any other functions until the function in progress is complete.

- 19. Observe that the display shows both quarters as in OVLAP. Watch the stripping progress through the lower spectrum. The MCA is multiplying the data in Q # 3 by the factor (0.5) and subtracting the result from the data in Q # 1. The result is the reduction of the data in Q # 1 by one-half. This can be verified by enabling INTEG once again and comparing the displayed integral to the value noted in step 15; it should be about one-half of that noted value.

- The data displayed in Q # 1 can be read out to a peripheral device by using the READ OUT function. See Section 6, Input/Output, for instructions.

- Press HOME. Note that the cursor has returned to channel 0, the first channel of the displayed segment.

- 22. Press CLEAR TIME. Look at the counts displayed for channel 0 (CL counts) and the ELAP (L) on the lower part of the display. Both should now read 0 (time has been cleared from memory). No data channels are affected by this function.

- 23. Press CLEAR DATA and note that all data has been cleared from memory. This function clears only the displayed section of memory, other sections are not affected by the operation. If CLEAR TIME had not been performed in the last step, enabling CLEAR DATA would have reset the two time channels, as well as all of the displayed data channels, to zero.

#### 3.4 MCS MODE

To see effect of MCS operation, use the same setup and control settings as for the preceding PHA experiment.

- 1. If there are data in the memory, press CLEAR DATA.

- 2. With the sample near the memory, press COLLECT.

- Increase the LLD control setting until no pulse storage takes place below the energy of interest, such as one or more of the peaks. Repeatedly pressing CLEAR DATA while increasing the LLD control will aid in finding the desired setting.

- Lock the LLD control, press COLLECT to stop acquisition and press CLEAR DATA to clear the memory.

- The ULD control can be decreased in the same manner if data acquisition is not wanted above a specific energy level.

- Press MCSR (for multiple sweeps through memory).

- Press COLLECT and observe the type of data displayed as a result of this different type of acquisition.

- 8. Press COLLECT to stop the MCS sweeps.

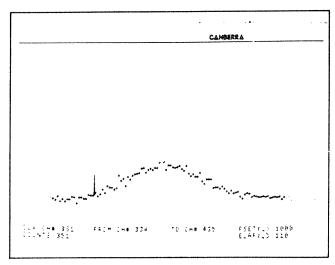

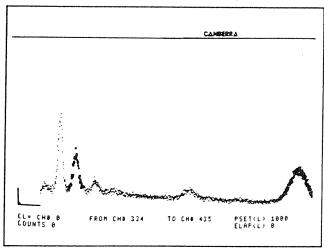

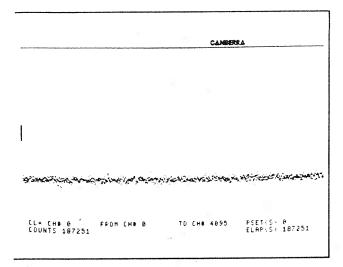

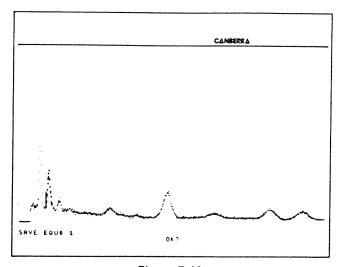

Figure 3-9

Typical MCSR Spectrum after 187 251 Sweeps

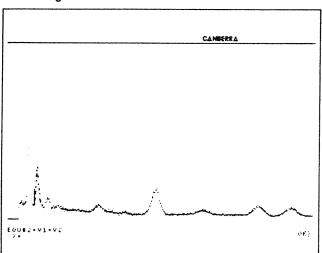

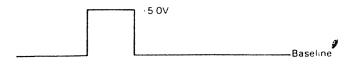

Figure 3-10 X2 Enabled. Note that the Horizontal Line of the top of the Display is absent.

## Section 4. Front Panel Functions

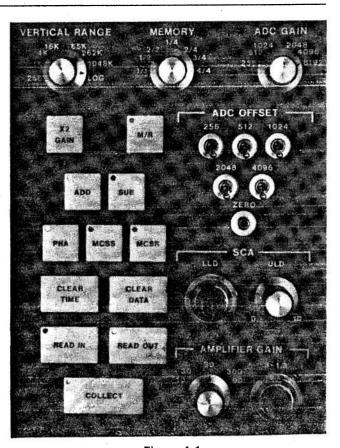

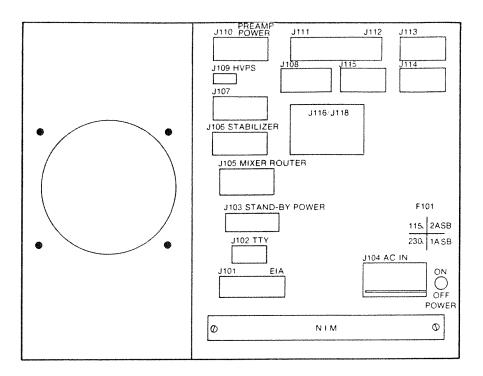

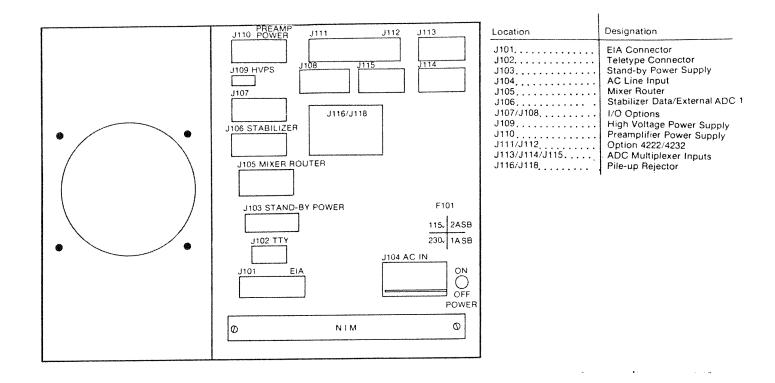

This section covers the controls found on the vertical Front Panel. These controls are concerned with the tasks of data acquisition and data input/output. Figure 4-1 provides a ready reference to the Control Panel layout.

The controls on the Keyboard (the horizontal panel) are used primarily in data manipulation and analysis. The description of their functions is covered in Section 5, following.

Starting with the functions in the upper left corner of the Front Panel, the controls are discussed as related groups from left to right and from top to bottom.

#### **4.1 VERTICAL RANGE AND X2 GAIN**

This eight position rotary switch selects the desired full-scale count value for the display, from 256 to 1048K (1 048 575) counts per channel, plus LOGarithmic display. Note that the highest setting is 2<sup>20</sup>-1 counts.

The switch is normally set so that the highest peak in the spectrum is no higher than the top of the display. If a channel accumulates more counts than can be displayed, the channel will "overflow." This is seen as a peak which appears to have its top cut off and is increasing in height again from the baseline. If a channel overflows the VERTICAL RANGE setting, the operator must increase the VERTICAL RANGE setting.

The X2 GAIN function multiplies the vertical display by 2 and provides an intermediate step in the full-scale ranges selected by the VERTICAL RANGE switch. 256 X2, for instance, gives a vertical viewing range of 128 counts per channel.

Figure 4-1 Front Panel

#### 4.2 MIXER/ROUTER

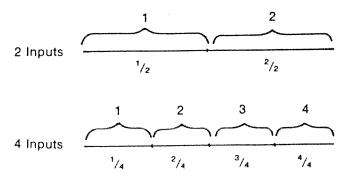

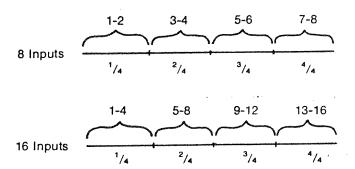

If the Model 4231 Mixer/Router Wiring or Model 4223 Multi-ADC Interface is installed in the analyzer, pressing the M/R button will allow the operator to choose how many inputs the analyzer is to accept. The dialogue will read:

NO. INPUTS \*2 4 8 16 OK?

Note: an Analyzer with a 1K memory will not offer the choice of 8 or 16 inputs.

Choosing the number of inputs with the \* will cause the Firmware to divide the full memory into the selected number of equal parts for separate data storage for each input.

To use the Analyzer with one input, the M/R button should not be used. If a Model 8220A Mixer/Router is being used, it should be disconnected from the system when a single input is desired.

Refer to the Model 8220A Mixer/Router's Operator's Manual or to the Model 4223 Multi-ADC operating instructions for further information.

#### 4.3 MEMORY

The MEMORY switch selects the section of memory to be:

- · addressed by the ADC for data storage

- · displayed by the CRT

- · read out of or read into

The operator may select full memory, either half or any of the quarters.

- · 1/1 refers to the full memory

- · 1/2 refers to the first half of the memory

- · 2/2 refers to the second half of the memory

- · 1/4 refers to the first quarter of the memory

- · 2/4 refers to the second quarter

- · 3/4 refers to the third quarter

- · 4/4 refers to the fourth quarter

Regardless of the memory segment chosen, the first two channels of the segment are used to register PHA Live and True time or MCS sweep count and Dwell Time code.

#### 4.4 ADC GAIN

This six-position rotary switch is used to establish the full scale resolution of the ADC, as discussed in the Introduction (Section 1.2.1.1). The ADC Gain is commonly set to equal the number of channels memory; that is, a 4K memory (4096 channels) would commonly use an ADC GAIN of 4096.

For finer resolution over a narrower energy range, the ADC GAIN switch, in conjunction with the ADC OFFSET, can be used to display the energy range of interest.

#### 4.5 ADC OFFSET

The ADC OFFSET establishes the relationship between memory channel zero and the ADC channel assignments. The effect of the Offset is to shift the spectrum by a selected number of channels.

For instance, if an ADC GAIN of 4096 is selected but only 1024 channels of memory are being displayed, then the upper 75% of the spectrum will not be stored in the memory. If the upper 25% of the spectrum is to be stored in the memory, the ADC OFFSET will have to be changed from zero to some number that will shift the spectrum by the desired number of channels.

In this example, an Offset of 3072 (1024 + 2048), which is the 4096 Gain less the 1024 memory size, will accomplish the shift by moving the zero channel of memory to ADC channel 3072. Converter pulses whose value is < 3074, will be discarded and pulses which convert to 3074 will be stored in the first data channel of the memory (channel 2). Note that the offset switches are additive.

With ADC Gains of 512 or 256, the Offset indicated by the switches is divided by 2 or 4, respectively.

#### 4.6 ZERO

The Analyzer is shipped with the ZERO control set for the memory size installed.

The ZERO control is a screwdriver-adjustable potentiometer which shifts the ADC zero relative to a zero energy (0 volts) input. This is done by shifting the spectrum by up to 5% of the ADC GAIN being used. It can be used like the ADC OFFSET to provide a fine control for positioning peaks.

The ZERO should be recalibrated each time the ADC GAIN is changed but is not critical. The result of not readjusting the ZERO will be a slight shift in the spectrum's peaks and slight change in linearity.

When performing experiments which require better linearity, channel zero of the analyzer is usually made to correspond to zero energy input. Appendix C lists three methods for accurately setting the ZERO control.

#### 4.7 ADD AND SUBTRACT

These two buttons enable either additive or subtractive data acquisition. If ADD is enabled, all new data acquired is added to existing data in the memory.

If SUBtract is enabled, all new data is subtracted from existing data in the memory. This mode is useful for subtracting a background or a standard reference spectrum from a previously acquired spectrum. Channels 0 and 1 are always additive.

The Series 40 default (power on) state automatically enables the ADD mode of data acquisition, as does System Initialization (see Section 2.2).

#### 4.8 PHA

Selects the Pulse Height Analysis (PHA) mode of data acquisition. Used in combination with either the ADD or the SUBtract mode (Section 4.7 above). See Section 1.2.1 for a description of the PHA function.

The Series 40 default (power on) state automatically enables the PHA mode, as does the Power Reset command.

#### 4.9 MCSS

Selects the Multichannel Scaling Single sweep (MCSS) mode of data acquisition. See Section 1.2.2 for a description of this mode. Used in combination with either the ADD or the SUBtract mode (Section 4.7 above).

If MCSS or MCSR acquisition is in progress, the firmware allows the operator to "STOP" or "ABORT" when terminating COLLECT. STOP = terminate at the end of the current sweep; ABORT = terminate immediately. ABORT is given as a choice only when the selected dwell time is equal to or greater than 2 msec.

#### 4.10 MCSR

Selects the Multichannel Scaling Recurring sweep (MCSR) mode of data acquisition. See Section 1.2.2 for a description of this mode, which differs from the MCSS mode only in that the analyzer will continue sweeping through the memory for a preset number of sweeps (see Section 5.2.2, MCS Preset) rather than a single sweep as in MCSS. Used in combination with either the ADD or the SUBtract mode (Section 4.7 above).

If MCSS or MCSR acquisition is in progress, the firmware allows the operator to "STOP" or "ABORT" when terminating COLLECT. STOP = terminate at the end of the current sweep; ABORT = terminate immediately. ABORT is given as a choice only when the selected dwell time is equal to or greater than 2 msec.

#### 4.11 LLD (Lower Level Discriminator)

This ten-turn, locking potentiometer is used to establish the lower energy limit for input signals that are to be converted by the ADC. Input signals that are below the LLD setting in amplitude are not converted. If signals below the LLD setting are above the factory set threshold, those signals will add an increment of deadtime equal to the signal's width.

For PHA operation, the LLD is usually set to a point just above the low energy noise that is normally present in the input signal. For MCS operation, the LLD is usually set just below the particular energy of interest.

### 4.12 ULD [Upper Level Discriminator]

A single-turn potentiometer which controls the upper energy limit for pulses to be processed by the ADC. Input signals that are above the ULD setting in amplitude are not converted. For MCS operation, the ULD is usually set just above the particular energy of interest.

#### 4.13 AMPLIFIER GAIN

The coarse and fine gain controls are provided to adjust the gain of the internal amplifier to the desired spectral energy range. Together they provide a gain range of 3 to 1170.

The coarse gain control is a five position rotary switch; the fine gain control is a ten-turn precision potentiometer that multiplies the setting of the coarse gain control by a variable factor which can be set as low as 0.3 or as high as 1.3.

The fine gain control is factory set to read 0.3 at its minimum setting so that its dial reads the variable factor directly, allowing the operator to set the amplifier's total gain with precision.

### 4.14 CLEAR TIME AND CLEAR DATA

These two pushbuttons are used independantly to either clear the first two channels in the memory segment chosen by the MEMORY switch (CLEAR TIME) or all channels in the chosen memory segment, including the time channels (CLEAR DATA).

CLEAR DATA is usually used to reset the entire memory to zero before starting a new experiment or a new run of the current experiment.

CLEAR TIME can be used to reset the two time channels to zero without erasing the existing data. The operator may wish to add or subtract new data using the same preset conditions as for the first data collection run.

#### 4.15 READ IN AND READ OUT

These pushbuttons control the input/output flow of data from or to a peripheral data storage device, such as a Teletype, a Cassette Tape or a Plotter. Their use is covered in detail in section 6.

#### 4.16 COLLECT

The COLLECT pushbutton controls data acquisition in the mode already chosen by the operator. (The PHA ADDitive mode, for instance.)

If MCSS or MCSR acquisition is in progress, the firmware allows the operator to "STOP" or "ABORT" when terminating COLLECT. STOP = terminate at the end of the current sweep; ABORT = terminate immediately. ABORT is given as a choice only when the selected dwell time is equal to or greater than 2 msec.

When Collect is enabled or disabled, the analyzer reads the position of the Memory switch to control data acquisition in that memory section. The Memory switch can then be changed at will in order to examine, manipulate or Read In/Read Out data in another section of memory.

## Section 5. Keyboard Functions

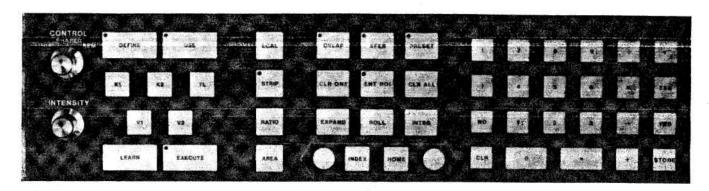

Figure 5-1 Keyboard Layout

The pushbutton functions on the Keyboard are concerned primarily with data manipulation. The pushbuttons on the left side of the Keyboard control the Model 4241 Define/Use option and the Model 4242 Learn/Execute option; the use of these options is covered in section 7.

Figure 5-1 provides a reference to the Keyboard layout.

#### 5.1 KEYPAD

The right-hand one third of the keyboard is the keypad. It is used to enter numbers in the X Register and functions in the Define/Use option by means of the numerals zero through nine and the STORE and CLR (clear) keys. The STORE key transfers the contents of the X Register into memory and the CLR key erases incorrect entries from the X Register. The CLR key also aborts an ILLEGAL ENTRY and clears that message from the display.

Additional to these keys, the keypad has left and right parentheses "(" and ")", the four arithmetic operators, an exponential notation key "EEX" and a radical key "\sqrt{"}".

#### 5.2 CONTROL

The three position CONTROL switch is provided for the Model 4272 GPIB and the Model 4271 and 4273 Computer Interfaces only. If none of these is installed, the switch will have no effect.

If the Model 4271, 4272 or 4273 option is installed, the CONTROL switch will function as follows:

- LOCAL—Allows only Keyboard control of the Series 40.

- REMote—Allows only remote (Computer) control of the Series 40.

- SHARED—Allows either Keyboard control or Computer control of the Series 40. Note that the analyzer cannot differentiate between Keyboard commands and Computer commands; it will respond to all commands in the order that they are received.

#### 5.3 OVERLAP

The OVLAP function is used to make a visual comparison between two spectra by superimposing a corresponding half or quarter memory over the currently displayed section of memory. Note that the function cannot be enabled if the MEMORY switch is in the 1/1 position.

The corresponding memory sections are set forth in the table below:

| Current display | Overlapped section |

|-----------------|--------------------|

| 1/2             | 2/2                |

| 2/2             | 1/2                |

| 1/4             | 3/4                |

| 2/4             | 4/4                |

| 3/4             | 1/4                |

| 4/4             | 2/4                |

The operator can modify the first half of the OVLAP dialogue to display another overlapped section of corresponding size simply by entering the desired number by way of the X Register. The second half of the dialogue is always the memory section currently being displayed.

The overlapped data is always displayed offset by 20% of the selected VERTICAL RANGE.

When the dialogue has been completed, pressing YES (in answer to OK?) will terminate the dialogue; the overlapped memory section will remain on the screen until the function is turned off by pressing OVLAP again.

After the Overlap dialogue has been completed, the MEMORY switch can be changed between halves or between quarters. This will allow other memory segments to be compared with the overlapped segment.

Note that if the MEMORY switch is changed outside of the original size memory segments, the function will turn itself off.

#### 5.4 TRANSFER

The XFER function allows the operator to copy data from one memory segment to another. Enabling XFER simultaneously enables OVLAP and displays the corresponding memory segment, as listed in section 5.8 OVERLAP, above. If the default parameters are acceptable, pressing YES will copy the data in the upper, overlapped, segment to the lower, current, segment.

The default parameters are alterable through the X Register to allow the overlapped memory segment to be changed to a segment other than the corresponding segment. The only restrictions are that the segment being transferred to must be chosen by the MEMORY switch and that the transfer can only take place between segments of the same size.

Note that Energy Calibration equations are transferred with the data but ROIs are not.

#### 5.5 PRESET

Each mode of data acquisition has its own default preset which can be changed as desired by the operator.

#### 5.5.1 PHA Preset

The Series 40 provides several preset conditions for the termination of PHA data acquisition:

- 1. Live or true time.

- 2. Counts in a specific channel.

- 3. Total Integral of a specific Region of Interest.

- 4. Total net Area of a specific Region of Interest.

- User defined with the Model 4241 Define/Use option. (Section 7.1.9 covers the user defined preset.)

Enabling PRESET brings up the following dialogue:

\*TIME(L) TIME(T) COUNTS INT AREA USER VAL= 1000 SEC x= OK?

The default state of 1000 seconds of Live time is displayed and may be changed through the X Register.

Using NO to advance the \* allows the choice of True time, any of the three computational presets or the user defined preset, which will bring up the question NEXT? in place of the question OK?

A response of YES (to NEXT?) changes the dialogue to allow the operator to enter, in the case of COUNTS, the desired number of counts and the specific channel that the analyzer is to monitor for that count level. The default parameters may be changed as usual through the X Register and the use of NO to advance the \*.

When the \* is at CHANNEL #, the current location of the cursor may be entered simply by pressing STORE.

If INTegral or AREA are chosen, the next line of dialogue will read

'INT (or AREA) 1000 COUNTS ROI FROM CH#0 TO CH#0

Enter the number of counts and press NO to advance the \*to ROI. Pressing STORE will enter the limits of the current ROI. If the \*is moved to FROM or TO, the ROI limits may be entered manually or by pressing STORE, which will enter the current cursor address.

Current ROI is defined at the end of Section 5.6.

It should be noted that, except in the case of Live time, acquisition does not stop exactly at the preset parameter. This is because Series 40 firmware prevents fraction of a second errors in the keeping of Live time. When the analyzer reaches preset, collection will stop at the next tick of the Live time clock.

A high Dead Time could cause a long real time to elapse before the next tick of the Live Time clock. In this case, Collect may be aborted by disconnecting the signal cable or by performing a Power Reset (section 2.2).

#### 5.5.2 MCS Preset

If MCSS or MCSR has been enabled, the PRESET dialogue will show:

DWELL (N\*101M USEC) N= 1 M= 2 SWEEPS = 1 (for MCSS) or SWEEPS = 0 (for MCSR)

The formula in parenthesis is read as "N" times 10 to the "M" power microseconds. The default preset, then, is set for 100 microseconds dwell time per channel.

The default state can be changed by way of the X Register and NO to advance the \*, subject to the following rules:

- 1. "N" can be set for 1 through 15.

- 2. When "M" is set to 9, the dwell will be expressed as "N" minutes.

- 3. When "M" is set to 10, the dwell will be expressed as "N" hours

- When "M" is set to 11, the dwell will be set to "N" times 10 minutes.

- When "M" is set to 15, the channel advance, and thus the dwell time per channel, will be under EXTernal control.

- Setting the preset to EXTernal will cause the firmware to count "N" External pulses before executing a channel advance.

The sweeps preset cannot be altered in the MCSS mode, but in the MCSR mode, the number of sweeps may be preset for the required number through the X Register. If the default parameter of zero is retained, the analyzer will interpret this as infinity. That is, the analyzer will continue to sweep through the memory until stopped manually or remotely. See section 4.16, Collect, for the two methods of MCS termination.

Note: in MCSR, the number of sweeps performed may, under some conditions, exceed the preset slightly.

#### 5.6 REGION OF INTEREST

The Series 40 has provision for entering Regions of Interest (ROIs) to mark significant peaks in the spectrum for later analysis and readout. To enter an ROI, simply

position the cursor at one limit of a peak with the Scan control, press ENT ROI, and Scan the cursor to the other limit of the peak.

Each data point that the cursor passes through while ENT ROI is enabled will be intensified to indicate the data that is within the ROI. When the further limit of the desired ROI is reached, release the Scan button and press ENT ROI once again to disable the function.

- 1. ENT ROI always causes the region through which the cursor passes to be set to the ROI state.

- 2. CLEAR ALL clears all ROIs from the displayed memory section.

- 3. CLEAR ONE, if the cursor is not located within a ROI, clears the current ROI.