# Dual Multi-Spectrum Storage (DMSS) User Manual

(Preliminary)

# Table of Contents

| 1. INTRODUCTION                        | .4       |

|----------------------------------------|----------|

| 2. CONTROLS AND CONNECTORS             | 6        |

| 2.1. Front Panel Connectors and Lights | 6        |

| 2.2 Rear Panel Connections             | 7        |

| 3. OPERATION                           | 8        |

| 4. HARDWARE SETUP                      | 10       |

| 5. PROGRAMMABLE SETUP FUNCTIONS        | 11       |

| 5.1. ICB Address                       | 11       |

| 5.2. Input Number                      | 11       |

| 5.3. Dwell Time                        | 11       |

| 5.4. Sweeps                            | 11       |

| 5.5. MSS Groups                        | 11       |

| 5.6. Active vs Passive                 | 12       |

| 5.7. Full Spectrum First in Memory     | 12       |

| A. SPECIFICATIONS                      | 13       |

| A.1 Inputs                             | 13       |

| A.2. Outputs                           | 13       |

| A.3. Manual Controls                   | - *- 13* |

| A.4. ICB Programmable Controls         | 13       |

| A.5. Front Panel Indicators            | 14       |

| A.6. Power Requirements                | 14       |

| A.7. Physical                          | 14       |

| B. REAR PANEL CONNECTORS               | 15       |

| C. SOFTWARE COMMAND STE              | RUCTURES | 16   |

|--------------------------------------|----------|------|

| C.1. Setup Information Storage       |          | 16   |

| C.2. DMSS Setup Utility              | • • •    | . 17 |

| C.3. MSS Spectral Extraction Utility |          | 18   |

and the second of

### 1. Introduction

And the second s

The DMSS module is a custom module designed for specific Canberra Applied Systems Applications. The name, DMSS, stands for Dual Multi Spectrum Storage. This module is built in the same form as Canberra's Instrument Control Bus Modules (ICB); however, it is not a fully supported module. This module does have the same interface requirements as the ICB modules, and therefore can only be used with an AIM module. Because it is not fully supported, the setup is not included in the standard Genie PC MID editor. Software setup is provided in the Genie PC Waste Assay Software with a separate editor for the DMSS module.

The DMSS module is a dual wide NIM module. It can handle the multi spectrum storage functions for two ADCs. It is set up and controlled through the ICB NIM communication bus.

The primary application for the DMSS module in the Applied Systems Division is to collect incremental spectra from rotating drums in Canberra's waste assay systems. The incremental information can be used to detect the degree of sample non-uniformity in the drum and in some cases can be used to improve the assay results. This manual is not intended to discuss the physics or algorithms associated with the non-uniformity detection or correction, it is only intended to explain the module and how to use it.

The primary functions for the module are as follows:

The first function is to create incremental spectra based on a particular dwell time. Assume that the dwell time is set for ten seconds. Then a count cycle which is 100 seconds long would increment 9 times and create a total of ten incremental spectra. The cycle can be started and reset with an index pulse. In this way data from a rotating measurement system can be summed over several rotational cycles.

The second function is to compress the spectral data. Since the AIM module is commonly used with 2 ADCs, each ADC can have a maximum of 32k channels of data. If the spectrum size is 4k, then the maximum number of incremental spectra which could be created is 8 without exceeding the 32k channels of data. However, if the 4k channel spectrum is compressed to a 2k channel spectrum, then 16 incremental spectra could fit into the 32k channel memory space. Compressing it to 1k spectra would permit 32 incremental spectra.

A third function is to create a full memory spectrum as well as the compressed spectra. Since some of the peak shape information is typically lost in a compressed spectra, there is typically a value in collecting a standard 4k or 8k channel spectrum. This function of the DMSS module splits the 32k memory range into two 16k sections. In one 16k section an uncompressed spectrum is collected over the full data collection interval. In the other 16k section the incremental compressed spectra are stored. The data storage can be set up so

that the full memory spectrum is first in memory or last in memory (i.e., in the first or second half of the memory range).

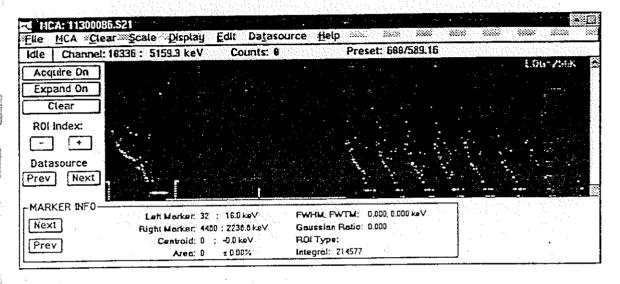

Figure 1.1 shows an MCA display for a 32k memory region with an 8k full spectrum on the left side of the MCA memory region and eight 2k DMSS spectra stored in the right 16k of the MCA memory display.

Figure 1.1 DMSS Spectrum

# 2. Controls and Connectors

# 2.1. Front Panel Connectors and Lights

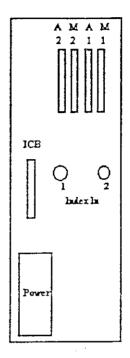

The picture below shows the front panel of the DMSS module. The functions of the BNCs are as follows:

Figure 2.1 Front Panel Connectors

\_ READY - The READY light is on when the DMSS is setup in the active mode.

ACQUIRE LED - The Acquire LED is on during acquisition.

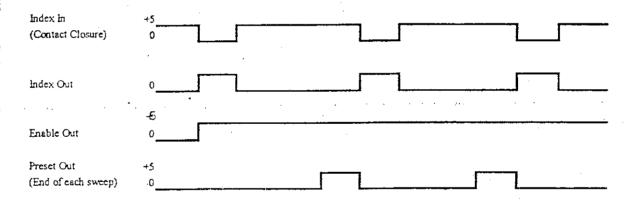

ENABLE OUT - This output is HIGH while the DMSS is acquiring live data

PRESET OUT - This signal is used for the calibration of the turntable.

INDEX OUT - This provides a buffered output version of the INDEX IN signal as accepted by the DMSS.

INDEX IN - This is used to reset the DMSS when counting over multiple rotations. The INDEX pulse from the turntable should be input here. This is falling edge triggered.

### 2.2 Rear Panel Connections

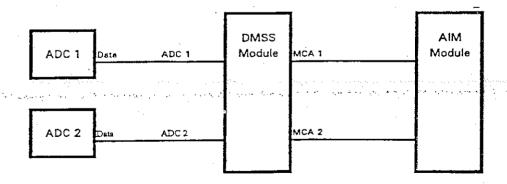

On the rear panel are the connections for ADC1 Input, ADC2 Input, MCA1 Output, MCA2 Output, and ICB Control. There are also INDEX In connectors for inputs 1 and 2. The signal descriptions for the ADC input connectors and the MCA output connectors are listed in Appendix B.

Figure 2.2 Rear Panel Connectors

The connection to ADCs and the AIM is shown schematically in Figure 2.3 for the data lines.

Figure 2.3 ADC - DMSS - AIM Data Connection

# 3. Operation

When acquisition is started on the MCA the DMSS module is enabled to look for Index pulses. The first pulse received will enable the ADC for spectral data acquisition. A full spectrum (size controlled by ADC gain) will start in half of the total memory and the first incremental spectrum in the other half of memory.

At the end of each dwell time the next spectrum will be enabled. Each Advance pulse will reset the enable to the first slice and increment the sweep counter. If an Advance pulse doesn't occur before the dwell time of the last slice, the DMSS module will start again at the first slice. The total dwell time for all slices should be slightly larger than the time between Advance pulses (see Dwell Time above) to allow the Advance signal to reset to the first slice just before the dwell time expires.

After the preset number of sweeps (rotations of the drum) has occurred the ADC acquisition will be disabled. When the MCA real time preset is reached all acquisition will stop.

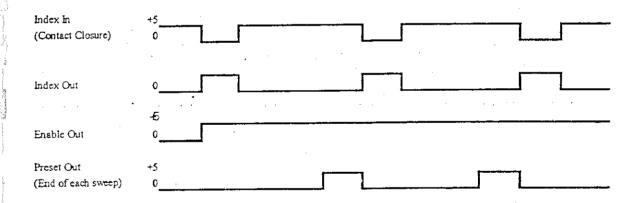

The relationship between the front panel signals is shown in Figure 3.1.

Figure 3.1 Front Panel Signals

In order to set the dwell time properly, it is advisable to place a radioactive source at a fixed position seen by the detector so that all group spectra should be identical. Then collect a spectrum.

If the dwell time is a little too short, the last group spectrum will be completed before the next index signal occurs. The DMSS will then start collecting data again in the first group. When the index signal does occur, it will again set data collection to the first group. This will be indicated by the total number of counts in the first group being higher than the rest of the groups. The first two groups will have higher counts than the rest if

## 3. Operation

process of settlings.

The second settlings of the second second

When acquisition is started on the MCA the DMSS module is enabled to look for Index pulses. The first pulse received will enable the ADC for spectral data acquisition. A full spectrum (size controlled by ADC gain) will start in half of the total memory and the first incremental spectrum in the other half of memory.

At the end of each dwell time the next spectrum will be enabled. Each Advance pulse will reset the enable to the first slice and increment the sweep counter. If an Advance pulse doesn't occur before the dwell time of the last slice, the DMSS module will start again at the first slice. The total dwell time for all slices should be slightly larger than the time between Advance pulses (see Dwell Time above) to allow the Advance signal to reset to the first slice just before the dwell time expires.

After the preset number of sweeps (rotations of the drum) has occurred the ADC acquisition will be disabled. When the MCA real time preset is reached all acquisition will stop.

The relationship between the front panel signals is shown in Figure 3.1.

Figure 3.1 Front Panel Signals

In order to set the dwell time properly, it is advisable to place a radioactive source at a fixed position seen by the detector so that all group spectra should be identical. Then collect a spectrum.

If the dwell time is a little too short, the last group spectrum will be completed before the next index signal occurs. The DMSS will then start collecting data again in the first group. When the index signal does occur, it will again set data collection to the first group. This will be indicated by the total number of counts in the first group being higher than the rest of the groups. The first two groups will have higher counts than the rest if

the dwell time is so short that the internal advance signal occurs before the index signal, and so on.

If the dwell time is a little too long, the last group spectrum will not complete the dwell time before the index signal occurs, and it will not have as many counts as the other spectra. If the dwell time is much too short, several of the last groups will have too few counts.

# 4. Hardware Setup

Since the DMSS is an ICB module, an address must be set in the NIM module in order for the ICB communication to recognize which module it is. This address should be a unique address in the range 0 - E (Hex) from other modules in that ICB Communication line. As with other ICB modules this is set by adjusting a multiposition switch on the circuit board. All other setup parameters are defined through the software using the ICB NIM protocol. The command structures are defined later in this manual.

# 5. Programmable Setup Functions

### 5.1. ICB Address

The ICB address assigned to the DMSS unit should be specified to send the commands to the proper unit.

### 5.2. Input Number

The input number specifies which channel of the DMSS module is being used.

#### 5.3. Dwell Time

The Dwell Time is the time in seconds (0.01 seconds resolution) that acquisition is active for each slice. This time is set in the 'DMSS Parameter Setup' screen and sent to the DMSS module with the 'MSS\_SET' batch command. The product of 'MSS groups' (also set in the setup screen) and 'Dwell Time' should be slightly longer (approximately 0.1 seconds) than the time to complete one revolution of the turntable. During acquisition the module will automatically increment to the next MCA memory slice at the end of each dwell time.

### 5.4. Sweeps

The Sweeps preset is the number of Advance (Index) pulses received (after acquisition enable) before acquisition is disabled. This preset is calculated from the Dwell Time, MSS groups and Real Time preset.

Sweeps = (Real Time / (Dwell Time \* MSS groups)) - 1

The MSS\_SET batch command calculates the Sweeps preset and writes it to the DMSS module.

### 5.5. MSS Groups

This parameter determines the number of incremental spectra to create.

When used with the application software the spectrum size will be determined by dividing the ADC conversion gain by the number of spectra to determine the spectrum size.

#### 5.6. Active vs Passive

The DMSS module can be set up through the software to operate in either the active or passive mode. In the active mode the DMSS capabilities are activated. In the passive mode the normal spectral data is passed through the system.

## 5.7. Full Spectrum First in Memory

This flag determines whether the full spectrum is stored in the first half of the memory or the second half.

Note: If there are two ADCs input to the AIM, it is best to set up the system so that the full spectrum is in the upper half of memory. This is because the very top of the AIM 64K memory has several hundred channels set aside for internal storage, and are not available for spectral data. If the full spectrum is in the upper half of the upper 32 K, and is less than 16K channels, the upper channels are not used, and there is no conflict. If the DMSS groups were placed in the upper half, the last group would be missing the upper part of its range.

Note: The total MCA memory size and the ADC conversion gain are setup for the ADC and AIM, using the MID editor.

# A. Specifications

### A.1 Inputs

INDEX IN - Accepts contact closure or negative unipolar pulses 0 to -5 volts minimum.

# A.2. Outputs

INDEX OUT - Provides positive logic pulse about 0.1 microseconds after trailing edge of INDEX IN signal.

ENABLE OUT - Provides positive logic pulse that is high during the acquisition time. It is the same as the ACQUIRE LED indication.

PRESET OUT - Provides positive logic pulse at the end of each sweep.

### A.3. Manual Controls

ADDRESS - Rotary switch selects 1 of 16 unique ICB adresses. It is accessible through opening in side cover.

### A.4. ICB Programmable Controls

ICB ADDRESS - 0 to F (hexadecimal)

MODE - TRANS (passive) or MSS (active)

DMSS INPUT NUMBER UNIT - 1 or 2

CHANNELS - 256 to 32768 in binary increments

ADC CONVERSION GAIN - 256 to 16384 in binary increments

NUMBER OF SWEEPS - 0 to 32768

NUMBER OF GROUPS - 1, 2, 4, 8, 16, 32

DWELL TIME - in centiseconds (0.01 second increments), 0 - 65536

DATA FIRST FLAG - 0 or 1 for full spectrum first or last in memory (0 is default)

# A.5. Front Panel Indicators

READY - Three-color LED; green when set up in active (MSS) mode, off when not set up or in passive (TRANS) mode.

ACQUIRE - Three-color LED; red during acquisition, off when not acquiring data.

## A.6. Power Requirements

| +24 V | +12 V |

|-------|-------|

| -24 V | -12 V |

| +6 V  |       |

# A.7. Physical

SIZE - Standard dual width NIM module 6.86 x 22.12 cm (2.70 in. X 8.71 in.) per DOE/ER-0457T.

NET WEIGHT - 1.5 kg (3.3 lb.)

SHIPPING WEIGHT - 2.6 kG (5.7 lb.)

### **B.** Rear Panel Connectors

This section lists the details of the DMSS rear panel interface and power connectors.

### **B.1. MCA Interface Connector**

This 34-pin ribbon connector (J102) provides all the necessary signals for connection to the AIM Negative true signals are shown with a trailing asterisk (ACEPT\*); all other signals are positive true.

| PIN  | SIGNAL   | PIN        | SIGNAL      |

|------|----------|------------|-------------|

| 1    | GND      | 2          | ACEPT*      |

| 3    | GND      | 4          | ENDATA*     |

| 5    | GND      | 6          | CDT* or CDT |

| 7    | GND      | 8          | ENC* or ENC |

| 9    | GND      | 10         | READY*      |

| 11   | GND      | 12         | INB* (INV*) |

| 13   | ADC13*   | 14         | ADCOO*      |

| 15   | ADC07*   | 16         | ADCOI*      |

| 17   | ADC08*   | . 18       | ADC02*      |

| 19   | ADCO9*   | 20         | ADC03*      |

| 21   | ADC 10*  | 22         | ADC04*      |

| 23   | ADC11*   | 24         | ADC05*      |

| 25   | ADC 12*  | <b>2</b> 6 | ADC06*      |

| 27 . | Reserved | 28         | Reserved    |

| 29   | BF*      | 30         | VGAIN       |

| 31   | BLLD     | 32         | VZERO       |

| 33   | BCB*     | 34         | ADC13X*     |

|      |          |            |             |

Interface Signal Functions

This section describes the function of each interface signal in detail. All input and output signals are TTL compatible. Unless otherwise noted, the input signal levels are:

Low =

$$0$$

to  $1.0$  volts

High =  $2.0$  to  $5.0$  volts

And the output signal levels are:

Low =

$$0$$

to  $0.5$  volts

High =  $3.0$  to  $5.0$  volts

All input and output signals considered to be a logic I for a high voltage level unless the signal name is followed by an asterisk (\*), in which case the signal is considered to be a logic 1 for a low voltage level.

# Rear Panel Connectors

| SIGNAL                                                                                                         | PIN  | DESCRIPTION                                               |

|----------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------|

| ADCQ0*··                                                                                                       | 14 · | OUTPUT: Binary data 2° (LSB)                              |

| ADC01*                                                                                                         | 16 . | OUTPUT: Binary data 2 <sup>1</sup>                        |

| ADC02*                                                                                                         | 18   | OUTPUT: Binary data 2 <sup>2</sup>                        |

| ADC03*                                                                                                         | 20   | OUTPUT: Binary data 2 <sup>3</sup>                        |

| ADC04*                                                                                                         | 22   | OUTPUT: Binary data 24                                    |

| ADC05*                                                                                                         | 24   | OUTPUT: Binary data 2 <sup>5</sup>                        |

| ADC06*                                                                                                         | 26   | OUTPUT: Binary data 26                                    |

| ADC07*                                                                                                         | - 15 | OUTPUT: Binary data 2 <sup>7</sup>                        |

| ADC08*                                                                                                         | 17   | OUTPUT: Binary data 28                                    |

| ADC09*                                                                                                         | 19   | OUTPUT: Binary data 29                                    |

| ADC10*                                                                                                         | 21   | OUTPUT: Binary data 21°                                   |

| ADC11*                                                                                                         | 23   | OUTPUT: Binary data 2 <sup>11</sup>                       |

| ADC12*                                                                                                         | 25   | OUTPUT: Binary data 2 <sup>12</sup>                       |

| ADC13*                                                                                                         | 13   | OUTPUT: Binary data 2 <sup>13</sup> (MSB)                 |

| ADC13X*                                                                                                        | 34   | OUTPUT: Binary data 2 <sup>13</sup> (Alternate MSB)       |

| ENDATA*                                                                                                        | 4    | INPUT (Enable Data): Used to enable the tri-state         |

|                                                                                                                |      | buffers driving the 14-bits of data onto the output lines |

|                                                                                                                |      | ADC00* through ADC13*.                                    |

| READY*                                                                                                         | 10   | OUTPUT (Data Ready): Indicates that data is available     |

|                                                                                                                |      | for transfer to the MCA. READY* will be reset after       |

|                                                                                                                |      | receipt of signal ACEPT*.                                 |

| ACEPT.*                                                                                                        | 2    | INPUT (Data Accepted): Signals the ADC that the data      |

|                                                                                                                |      | has been accepted by the MCA. ACEPT* may reset            |

|                                                                                                                |      | when READY* resets (handshake).                           |

| INB*                                                                                                           | 12   | OUTPUT (Inhibit): This signal indicates that the data     |

|                                                                                                                |      | available for transfer to the MCA is invalid and,         |

| •                                                                                                              |      | although the data transfer must be completed, the data    |

|                                                                                                                |      | itself should be discarded by the MCA.                    |

| ENC* or                                                                                                        | 8    | INPUT (Enable Converter): This signal enables or          |

| ENC                                                                                                            |      | disables the ADC module. A jumper option (W3) allows      |

|                                                                                                                |      | selection of polarity. ENC = logic 1 enables ADC          |

|                                                                                                                |      | operation. ENC = logic 0 prevents the ADC from            |

| er en ser en la la companya de la c |      | reopening the linear gate thereby inhibiting further      |

|                                                                                                                |      | operation.                                                |

| CDT* or                                                                                                        | 6    | OUTPUT (Composite Dead Time): This signal indicates       |

| CDT                                                                                                            | ÷    | the time when the ADC or connected amplifier is busy      |

|                                                                                                                |      | and cannot accept another input event. It is used to gate |

|                                                                                                                |      | the live time clock circuit in the MCA. A jumper option   |

| •                                                                                                              |      | (W8) allows selection of polarity.                        |

| BF*                                                                                                            | 29   | OUTPUT: This signal is set true at peak detect time and   |

|                                                                                                                |      | remains true until the leading edge of ACEPT*. This       |

|                                                                                                                |      | signal is meaningful in the NON-OVERLAP mode only.        |

|                                                                                                                |      |                                                           |

| BCB*              | 33<br>-      | OUTPUT: This signal is set true at peak detect time and remains tare until READY* is set true. It represents the conversion time of the internal ADC.                                                                                                                                             |

|-------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BLLD              | 31 .         | OUTPUT: This signal is set true when the input pulse rises above the ADC Threshold level and remains true until the trailing edge of ACEPT*.                                                                                                                                                      |

| VZERO<br>(Analog) | 32           | INPUT: This analog signal controls the ADC zero and it is normally provided by the spectrum stabilizer. The ZERO shift of the ADC is ±3% for a                                                                                                                                                    |

|                   |              | ±5 volt input signal. A more positive level on this signal causes spectral peaks throughout the spectrum to move downward.                                                                                                                                                                        |

| VGAIN             | 30           | INPUT: This analog signal controls the ADC gain and is normally provided by the spectrum stabilizer. The GAIN shift of the ADC is ±3% for a ±5 volt input signal. A more positive level on this signal causes spectral peaks at the upper end of the spectrum to move downward (lowers the gain). |

| GND .             | 1,3,5,7,9,11 | DC common for all interface signals.                                                                                                                                                                                                                                                              |

# **B.2. ICB Interface Connector**

This 20-pin ribbon connector(J103) provides all the necessary signals for connection to the Instrument Control Bus (ICB). Negative true signals are shown with a trailing asterisk (LWE\*); all other signals are positive true.

| PIN | SIGNAL | PIN | SIGNAL |

|-----|--------|-----|--------|

| 1   | GND    | 2   | LD0    |

| 3   | LD1    | 4   | GND    |

| 5 , | LD2    | 6   | LD3    |

| 7   | GND    | 8   | LD4    |

| 9   | LD5    | 10  | GND    |

| 11  | LD6    | 12  | LD7    |

| 13  | GND    | 14  | LWE*   |

| 15. | GND    | 16  | LDS*   |

| 17  | GND    | 18  | LAS*   |

| 19  | GND    | 20  | LSRQ*  |

### **Interface Signal Functions**

This section describes the function of each interface signal in detail. All input and output signals are TTL compatable. Unless otherwise noted, the input signal levels are:

Low = 0 to 1.0 volts High = 2.0 to 5.0 volts

# C. Software Command Structures

# C.1. Setup Information Storage

The setup information for a single input of a DMSS module is stored in the detector datasource CAM file (i.e., two setup files are required to set up both inputs). The uses of the parameters are as follows:

| • | CAM_T_MCSADDRESS | \ ICB address (0-F)                             |

|---|------------------|-------------------------------------------------|

| • | CAM_L_MCSINPUT   | DMSS input number (1 or 2)                      |

| • | CAM_L_CHANNELS   | Total MCA memory size (channels; <= 32768)      |

| • | CAM_L_CNVGAIN    | ADC conversion gain (<= 16384)                  |

| • | CAM_L_MCSGROUPS  | Number of MSS groups (1;2;4;8;16;32)            |

| • | CAM_F_DWELL      | Dwell time (centiseconds, < 65536)              |

| • | CAM L MCSDATAIST | MSS data first flag (default is ADC data first) |

A sample Genie PC Waste Assay Software editing screen for this information is shown below. The values are then inserted into the detector datasource with the PARS command.

| DMSS Parameter Editor   |             | 1,24 - 39   |

|-------------------------|-------------|-------------|

| DMSS ICB address:       | 0           | <b>X</b>    |

| DMSS input:             | in memory   | <b>]*</b> ] |

| Input total memory:     | 8192        |             |

| ADC conversion gain:    | 8192        |             |

| MSS groups:             | 8           | ž           |

| Dwell time: (12.2)      | 0.75        | sec.        |

| O <u>k</u> <u>C</u> ano | el <u>t</u> | telp        |

Figure C.1. DMSS Editor

### C.2. DMSS Setup Utility

It is suggested that a batch command be written to set up the DMSS module. REXX or DCL could be used to setup the module; however, since setup must be done once per input per acquisition, system throughput will be optimized using a batch command.

The command has the following format:

MSS\_SET detector /MODE=<mode> /PRESET=<real time value>

#### where

Strategieren der Strate

- detector is the name of the detector datasource into which the setup parameters are stored and into which the DMSS will acquire data.

- mode sets the mode of the DMSS: 'TRANS' for "transparent" acquisition (passive mode), where no MSS is done; and 'MSS' for normal MSS acquisition (active mode).

The other parameters are set by inserting them into the detector datasource with a PARS command.

The program should, in summary:

- 1. Obtain and verify all input arguments.

- 2. Open the setup file and read out the DMSS parameters.

- 3. Open the detector.

- 4. Verify that the detector is not in acquire; if it is, exit with an error status.

- 5. Write parameters to the ICB registers for the designated input (note that some conversion of the values is required, as described below); the registers for the other input on the DMSS should not be modified. The DMSS mode (MOP0 and MOP1) should be set according to mode.

- 6. Close the detector and exit.

The parameters stored in the file are the minimal ones required, from which all other DMSS settings can be derived:

- The MSS conversion gain is (MCA memory/2)/MSS groups

- The MSS compression factor is ADC gain/MSS gain

- The number of preset sweeps is (preset time/(dwell time \* MSS groups)) 1

# C.3. MSS Spectral Extraction Utility

During data acquisition the spectrum appears as one large complex spectrum, with a full spectrum in one half, and the incremental spectra in the other half. In order to analyze all the individual spectra, each spectrum must be placed in its own file. In addition, the real and live times must be adjusted since the DMSS will not acquire data until the first index pulse, and will stop after the preset number of pulses; this "dead" time is not accounted for in the MCA's real and live times.

A batch command will perform this extraction process. Its calling format is:

DMSSEXTR input setupfile outputroot calibration

#### where

- input is the name of the datasource which contains the DMSS data.

- setupfile is the name of the DMSS setup file which controlled the acquisition of the data in input.

- outputroot is the string which determines the format of the new files to be created. outputroot will be used in a C sprintf command to generate the output file names, where an integer value indicates the spectrum: 0 for the full spectrum, 1 for the first DMSS spectrum, 2 for the second, etc.

- calibration is the name of the datasource which contains, at a minimum, the energy and shape calibration information for the detector.

The operation of the utility is as follows:

- 1. Read in the arguments.

- 2. Open setupfile and read the DMSS setup parameters.

- 3. Open input and read in the spectrum, the acquisition start time, and the elapsed times.

- 4. Calculate the actual live and real times:

```

treal = preset sweeps * dwell * groups

tlive = live - (real - treal)

```

- 5. Open calibration and get the energy calibration coefficients

- 6. Generate the name of the main spectrum (number 0) and duplicate calibration to create this file. Write just the "raw" (i.e., ADC portion) of the spectrum to this file. Write treal and thive and the acquisition start time; then close.

- 7. Calculate new energy coefficients for the MSS spectra:

cf is the compression factor (for example, if ADC is 8K, MSS is 2K, cf = 4)

```

new offset = old offset

new slope = old slope * cf

```

```

new quad = old quad * cf**2

new cubic = old cubic * cf**3

```

- 8. The live and real time for the entire spectrum must be apportioned among the MSS groups (in the equations below, n is the number of groups). Rather than dividing the times equally, the live time is divided weighted by the number of counts in the spectrum for that MSS group:

- a) Calculate the number of counts in each MSS group (Si)

- b) Sum the counts of the individual groups (S<sub>i</sub>)

- c) Calculate a weighting factor W<sub>i</sub> for each group: S<sub>i</sub>/(S<sub>t</sub>/n)

- 9. For each MSS group:

Months of the Control of the Control

- a) Calculate the name of the spectral file (spectrum numbers 1 through n)

- b) Duplicate calibration to create the file

- c) Delete the PHA data area and recreate it with the proper number of channels

- d) Write the spectral data for the current group

- e) Write the acquisition start time and the weighted live and real times for this group: treal-(treal\*((treal-tlive)/treal)\* W<sub>i</sub>) and treal/n, respectively