# DUAL COUNTER TIMER Model 2071A

**Operator's Manual**

| . *  |

|------|

|      |

|      |

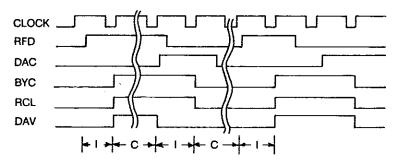

| <br> |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

| :    |

|      |

|      |

| Í    |

# **Table of Contents**

| Page                                                                                                                                                                                                                                                                                                                                                                              | Page                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. INTRODUCTION 1.1 Introduction                                                                                                                                                                                                                                                                                                                                                  | 7. THEORY OF OPERATION 7.1 Eight Decade Counting Channel                                                                                                                                                                                                                                                                                                                                                      |

| 2. SPECIFICATIONS         2.1 Inputs       1         2.2 Input/Output       2         2.3 Front Panel Controls       2         2.4 Performance       2         2.5 Internal Controls       2         2.6 Power       2         2.7 Physical       2         2.8 Option: 2071-01       2         GPIB (IEEE 488) Interface       2         2.9 Option: 2071-02                     | 7.2 Crystal Based Time Generator       .17         7.3 Preset Counter       .17         7.4 Six Decade Liquid Crystal Display       .17         7.5 Control       .17         7.6 Power Supply       .18         7.7 Daisy Chain Option       .18         7.8 GPIB Interace Option (Talker)       .19         7.9 GPIB Option Functional Description       .21         7.10 Typical Bus Interchange       .22 |

| Canberra NIM Daisy Chain Interface                                                                                                                                                                                                                                                                                                                                                | ## FIGURES  3.1 Front Panel                                                                                                                                                                                                                                                                                                                                                                                   |

| 4. OPERATION         4.1 Display Annunciators       7         4.2 Preset       7         4.3 Event Counter       7         4.4 Time Counter       7         4.5 Dual Counter       7         4.6 Single/Recycle       7         4.7 Reset       8         4.8 System Operation       8         4.9 Gate A and B       8         4.10 Enable       8         4.11 Overflow       8 | 6.2 GPIB Connector Wiring                                                                                                                                                                                                                                                                                                                                                                                     |

| 5. DAISY CHAIN INTERACE 5.1 System Setup 9 5.2 Printing System 9 5.3 Computer Control 9 5.4 Daisy Chain Jumper Options 9 5.5 Typical Systems 10 5.6 Using the Model 1488 Scanner 10 5.7 Field Installation of the Daisy Chain Option 10 5.8 Control In/Out Connectors 11                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6. INTERACTION OF MODEL 2071A with the GPIB 6.1 General Description of GPIB                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | 1 41 |  |  |            |

|---|------|--|--|------------|

|   |      |  |  |            |

|   |      |  |  | •          |

|   |      |  |  |            |

|   |      |  |  |            |

|   |      |  |  | 7 .        |

|   |      |  |  |            |

|   |      |  |  | i          |

|   |      |  |  |            |

|   |      |  |  | Ì          |

|   |      |  |  |            |

|   |      |  |  |            |

|   |      |  |  | -          |

|   |      |  |  |            |

| • |      |  |  | 1 .        |

|   |      |  |  | , .        |

|   |      |  |  |            |

|   |      |  |  | 1          |

|   |      |  |  |            |

|   |      |  |  | { }        |

|   |      |  |  |            |

|   |      |  |  |            |

|   |      |  |  | 100        |

|   |      |  |  |            |

|   |      |  |  | ι.         |

| • |      |  |  |            |

|   |      |  |  | {          |

|   |      |  |  | ) ;        |

|   |      |  |  |            |

|   |      |  |  | 1          |

|   |      |  |  |            |

|   |      |  |  |            |

|   |      |  |  | 1          |

|   |      |  |  |            |

|   |      |  |  | <b>\</b> / |

|   |      |  |  | y 44       |

|   |      |  |  | )          |

|   |      |  |  | 1          |

|   |      |  |  |            |

|   |      |  |  | 1          |

|   |      |  |  | 1 ;        |

|   |      |  |  |            |

|   |      |  |  | 1          |

|   |      |  |  |            |

|   |      |  |  |            |

|   |      |  |  |            |

|   |      |  |  | {          |

|   |      |  |  | 1 .        |

|   |      |  |  |            |

|   |      |  |  |            |

|   |      |  |  | 1.         |

|   |      |  |  |            |

|   |      |  |  | 1          |

|   |      |  |  |            |

|   |      |  |  |            |

|   |      |  |  | 1          |

|   |      |  |  |            |

|   |      |  |  | 1          |

|   |      |  |  |            |

|   |      |  |  | 1          |

|   |      |  |  | T.         |

|   |      |  |  |            |

|   |      |  |  | 1          |

|   |      |  |  | į<br>t     |

|   |      |  |  |            |

# Section 1. Introduction

The Canberra Model 2071A Dual Counter/Timer provides, in a single width NIM module, two eight decade counters, a crystal time base, and presetting logic. Normal operation is as a preset timer and event counter, or as a preset event counter and timer. However, the Model 2071A may also operate as a dual counter plus preset timer without display of the preset data.

Both count INputs accept fast negative NIM or positive pulses, jumper selectable. A discriminator is provided allowing positive inputs to be compatible with unipolar and bipolar linear signals or TTL logic pulses. The front panel positive DISCriminator covers an input range of +100 mV to +10 V permitting selective counting, eliminating spurious counting from noise or other erroneous pulses.

The Model 2071A accommodates input counting rates of 100 million counts per second (100 MHz) for negative inputs and 25 million counts per second (25 MHz) for positive inputs.

The internal crystal time base provides increments of 0.01 seconds or 0.01 minutes, and live time gating at one microsecond resolution.

Display of either counter's content is accomplished with a six digit Liquid Crystal Display. The LCD includes eight annunciators which describe the display and dynamic state of the unit. Automatic x100 range shift provides an indication of the six most, or six least significant digits.

Preset control is accomplished with a three digit thumb-wheel switch providing a preset range from one to  $99 \times 10^6$  increments.

The SINGLE/RECYCLE mode switch provides a method to automatically place the unit or system back into the counting mode ten seconds or 100 microseconds, jumper selectable, after preset or termination of the count mode is reached.

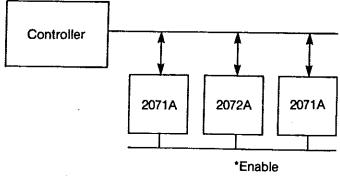

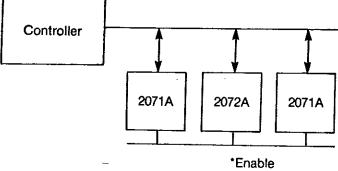

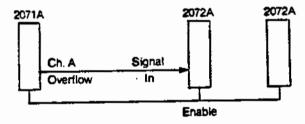

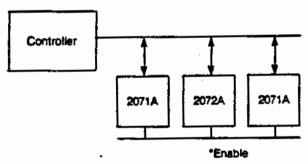

Master-Slave system operation can be accomplished via the front or rear panel interconnection of the ENABLE signal, or by either of the two optional I/O interfaces.

The Canberra NIM Daisy Chain option provides interfacing to all Canberra printing counters, timers, and readout scanners. Standard with the NIM Daisy Chain option is a Read Out Buffer capability such that with any number of counting modules a total of only 100 microseconds dead time is required.

The alternate Canberra GPIB (IEEE-488) option provides interfacing to a GPIB bus, and allows a GPIB Controller to start, stop, and read out counting systems.

A convenient ENABLE output will allow the Model 2071A to start, stop, and reset single or multiple combinations of other Canberra Series 2000 counting modules.

For an accumulation of data in channel A, a jumper can be changed to prevent the resetting of channel A.

External connection to the A or B GATE inputs will permit gating of incoming pulses when in the preset count mode, and gating of the time base for channel A or B, jumper selectable, when in the preset time mode. In this mode the gate provides one microsecond resolution. Thus when a system busy signal is connected to this input, the Model 2071A will provide extremely accurate dead time corrections.

# Section 2. Specifications

#### 2.1 INPUTS

A and B IN - Front panel BNC connectors accept positive linear, TTL, or negative NIM fast logic signals, jumper selectable. Positive operation accepts unipolar, bipolar, or TTL signals; amplitude: 0 to  $\pm$ 10 V,  $\pm$ 12 V maximum; input amplitude must exceed the adjustable discriminator level for 20 nsec to be counted. Negative NIM fast logic amplitude:  $\pm$ 0.6 V to  $\pm$ 1.6 V; minimum width 4 nsec below  $\pm$ 0.6 V; input rise and fall times: 1 nsec to 300 nsec;  $\pm$ 2 in  $\pm$ 1 k ohms

dc for positive signals and  $\approx$  50 ohms for negative signals. GATE B - Counting control for channel B or time channel, jumper selectable; with time gate selected, 1  $\mu$ sec time resolution can be obtained; shipped as channel B counting control. Amplitude: + 4 to + 5 V or open circuit allows counting; zero to + 0.8 V inhibits counting;  $Z_{in} \approx$  100 k ohms to + 5 V bus. When used as time gating, system busy can be used for accurate dead-time correction.

## 2.2 INPUT/OUTPUT

GATE A/ENABLE - Front panel BNC connector having a multifunction capability; GATE A or ENABLE, internally selected with jumper plug; shipped in ENABLE position.

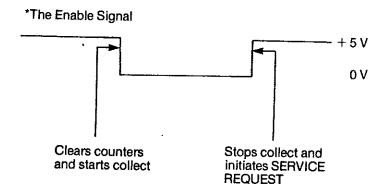

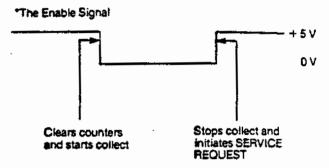

GATE A - With respect to channel A, same as GATE B. ENABLE - Bidirectional as input or output, open collector function, logic "0" OR; sinks 20 mA, sources from 4.7 k ohm to + 5 V bus.

As an Output - Provides counting control to other 2071A, 2072A or compatible modules; 0 to + 0.8 V enables counting, +4 V to +5 V disables counting As an Input - 0 to + 0.8 V enables counting mode; + 4 V to + 5 V or open circuit disables counting mode.

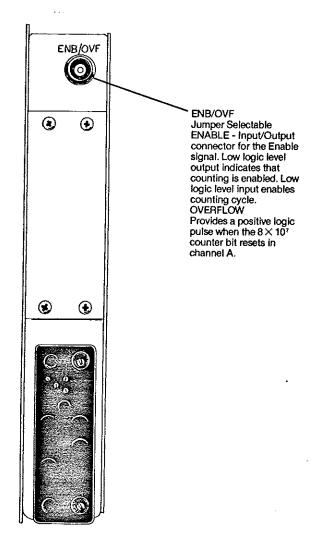

ENB/OVF - Rear panel BNC connector having a multifunction capability, ENABLE or OVERFLOW; internally selected with a jumper plug; shipped in the OVF position.

OVF - Outputs a + 5 V pulse coincident with the eighth decade reset; rise and fall times < 200 nsec; width 0.3  $\mu$ sec nominal; dc coupled; sinks 5 mA, sources 2.5 mA at 2.5 V; internal jumper selects channel A or B as source. Shipped in the channel A position.

ENABLE - Bidirectional as input or output, open collector function, logic "0" OR; sinks 20 mA, sources from 4.7 k ohm to + 5 V bus.

As an Output - Provides counting control to other 2071A, 2072A or compatible modules; 0 to + 0.8 V level enables counting, + 4 V to + 5 V disables counting. As an Input - 0 to + 0.8 V enables counting mode; + 4 V to +5 V or open circuit disables counting mode.

#### 2.3 FRONT PANEL CONTROLS

START/STOP - Two-position momentary toggle switch initiates or terminates a counting sequence.

RESET - Manual push-button resets both counters to zero. SINGLE/RECYCLE - Two-position toggle switch selects single or recycle mode of operation upon reaching a preset condition.

0.01 SEC/COUNT B/0.01 MIN - Channel B time base or count selector; three-position toggle switch to select 0.01 seconds, 0.01 minutes, or the external B IN as the B counter and preset function. When time is selected, channel A counts external events through A IN. When Count B is selected, channel A counts time in 0.01 second intervals. An additional capability selected by internal jumpers provides a time preset, and event counting in channel A and B. In this case time is not available for display or readout.

A/B DISPLAY SELECT - Two-position toggle switch selects which counter's contents are displayed on the LCD. PRESET NM × 10P - Three-digit thumbwheel switch for channel B preset. M is units, N is tens, P is the power of 10. N. and M range from 0 to 9; P has a range of 0 to 6; N = M = 0disables the Preset function.

# 2.4 PERFORMANCE

CAPACITY - Eight decades per channel, allowing 108 -1 counts in each.

COUNT RATE - 100 MHz max., negative; 25 MHz positive. PULSE PAIR RESOLUTION - 10 nanoseconds, negative; 40 ns positive.

CRYSTAL TIME BASE ACCURACY - ± 0.0025% over operating temperature range.

TEMPERATURE OPERATING RANGE - 0 to 50°C. PRESET COUNT CHANNEL - Limited to 1 MHz count rate; pulse width minimum 300 nsec.

INDICATORS - Six digit Liquid Crystal Display with auto (x100) shift for displaying six most-significant digits. Eight annunciators on LCD describe the display. These are: OF (overflow), x100, CNT, MIN, SEC, A, B, decimal point. Active counting is indicated by CNT, MIN, or SEC blinking. Leading zeroes are suppressed.

#### 2.5 INTERNAL CONTROLS

STANDARD JUMPERS (When set, perform the following):

- Inhibit reset of channel A when starting. In this mode channel A accumulates counts and is reset only by the manual pushbutton.

- Select OVERFLOW or ENABLE as the function of the rear panel connector.

- Select OVERFLOW output from channel B instead of channel A.

- · Permit counting in both channels. In this mode the module may still be preset on time, but the time cannot be read out.

- Allow a pulse on ENABLE INPUT to start the module.

- Change recycle time from 10 sec to 100 μsec.

- Select GATÉ A or B to gate the time channel.

Select GATE A or ENABLE as the function of the front panel connector.

- Select input A and B to accept positive linear and TTL, or negative NIM signals.

# 2.6 POWER

| 2071 | A Alone | with-01 | with -02 |

|------|---------|---------|----------|

| +12  | 120 mA  | 155 mA  | 123 mA   |

| -12  | 200 mA  | 235 mA  | 203 mA   |

| +24  | 35 mA   | 35 mA   | 35 mA    |

| -24  | 0       | . 0     | 0        |

#### 2.7 PHYSICAL

SIZE - Standard single width NIM module;  $3.43 \times 22.12$  cm (1.35 × 8.71 inches) per TID-20893 (rev. A) NET WEIGHT - 0.94 kgs (2.0 lb.) SHIPPING WEIGHT - 3.2 kgs (7.0 lb.)

# 2.8 OPTION: 2071-01 **GPIB (IEEE 488) INTERFACE**

#### A. Features

- Asynchronous ASCII data transmission bit parallel. character serial

- Uniquely addressable, switch controlled

- Talk/Listen mode

- Talk Only mode

- Auto recycle minimizes readout dead time

- Field installable

- · Form feed or carriage return at end of word

## B. Description

The General Purpose Interface Bus links a Canberra NIM counting module into the IEEE 488 standard communications network. As a Listener, this interface receives Start, Stop, and Readout commands from a controller. As a Talker, it supplies its accumulated data to a peripheral device. A Talk Only mode provides a controllerless means for a single module to read out to a peripheral Listener. The Auto Recycle mode allows the selected module to place itself (and the rest of the Canberra counting system) back into the count mode at the conclusion of its readout, thus minimizing system dead time. A side panel cutout provides

access to Set or Verify a Talk/Listen Address, select Talk Only mode, enable Auto Recycle, or select Form Feed/Carriage Return at the end of a word. This interface is a single PC board with a connector that allows convenient field installation.

C. Specifications

SIGNALS - The input/output signals on the GPIB connector are TTL compatible. True equals 0 to + 0.4 V, False equals +2.5 to +5 V.

CONTROLS - Side-panel cutout provides access to:

Address select switches (5)

Talk-Listen/Talk Only switch

Auto Recycle switch

FF/CR switch

Internal jumper enables Stop command response (DC 2). CONNECTOR - Standard GPIB connector on rear panel. CONFORMITY - Option 01 contains the following subset of capabilities (for explanation see IEEE-488 Standard) SH1, AH1, T1, TE0, L0, LE0, SR1, RL0, PP0, DT0, C0, DC0/DC2 selectable.

D. General Description of GPIB

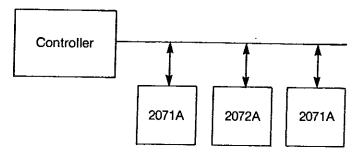

The General Purpose Interface Bus is a link or network by which system components communicate with each other. Each system participant performs at least one of three roles: Controller, Talker, or Listener.

A Controller manages bus communications primarily by directing or commanding which devices are to send data to other devices (Talker), or receive data from other devices (Listener) during an operational sequence. A controller may also be interrupted or it may command specific action between devices.

The GPIB consists of 16 lines which are grouped into three sets according to function; there are 8 data lines, 3 control lines, and 5 general management lines. The 8 data lines carry ASCII characters (bit parallel) asynchronously; the control lines provide a data transfer handshake compatible with both slow and fast devices; the bus management lines allow initialization, interrupts, and special controls.

#### E. Cable

One Canberra Model C2071-2 GPIB Data/Control cable 0.6 m (2 feet) long is supplied for connection to the GPIB bus.

# 2.9 OPTION: 2071-02 CANBERRA NIM DAISY CHAIN INTERFACE

### A. Features

- Synchronous BCD data transmission bit parallel, character serial

- Readout sequence determined by interconnect order

- Field installable

- System control via individual Start, Stop, and Reset signals

- Compatibility with Canberra counters and scanners

- Read Out Buffer

#### B. Description

The Canberra NIM Daisy Chain Interface Option provides the basic 2071A module with a readout/control capability compatible with previous Canberra data-acquisition series modules.

Read Out Buffering is available by moving jumper DD to position CC. This sets the Recycle time to 100 microseconds and only needs to be carried out on the 2071A selected as Master. Operating the Master, and hence the entire system, in the Recycle mode provides a minimal (100 microsecond) dead time buffered counting system.

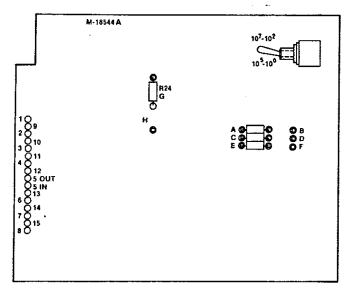

The problem of data transfer from the eight digit 2071A to the standard six-digit system is handled by a toggle switch on the interface board. It selects either the six mostsignificant digits or the least-significant digits. Two digits are lost in either case.

Control signals, Start, Stop, and Reset are received only if the unit is to be a system slave. A master until will generate Start, Stop, and Reset. This logic is under internal jumper control.

C. Signals

CONTROL IN - Accepts Start, Stop, Reset, and Print pulses (5 V negative going from + 5 V level, rise time 500 nanoseconds maximum, width 1.0 microseconds minimum. Also HOLD command (dc level change from +5 V to +0.5 Vmaximum during printout) is accepted. Rear panel 15-pin

"D" connector (Amphenol 17-10150). CONTROL OUT - Provides Start, Stop, and Reset commands (5 V negative going pulses from +5 V level, rise time 500 nanoseconds maximum, width 1.9 microseconds minimum). Data output information is presented in the form of Serial BCD (logic 1 = +4 to +5 V dc, logic 0 = 0 to +0.5 V dc). This connector also provides the "next unit" Print command; eighth and successive Print command pulses are routed out via a logic gate. All control lines except Print command are wired directly between Control In and Control Out connectors. Rear panel 15-pin "D" connector (Amphenol 17-20150).

#### D. Controls

SIGNIFICANT DIGIT SWITCH (107 - 102/105 - 100) - 107 -102 position selects readout of the six most significant digits of the eight-digit word. 105 - 100 position selects readout of the six least significant digits of the eight-digit word. Jumpers allow the Model 2071A to act as a system master or as a slave.

# E. Cable

One Canberra Model C1404-2 Data/Control cable 0.6 m (2 feet) long is supplied for connection to other Canberra data acquisition series modules.

# Section 3. Controls and Connectors

This section outlines the uses of the Model 2071A's controls and connectors. A complete listing of signal parameters will be found in Section 2, SPECIFICATIONS.

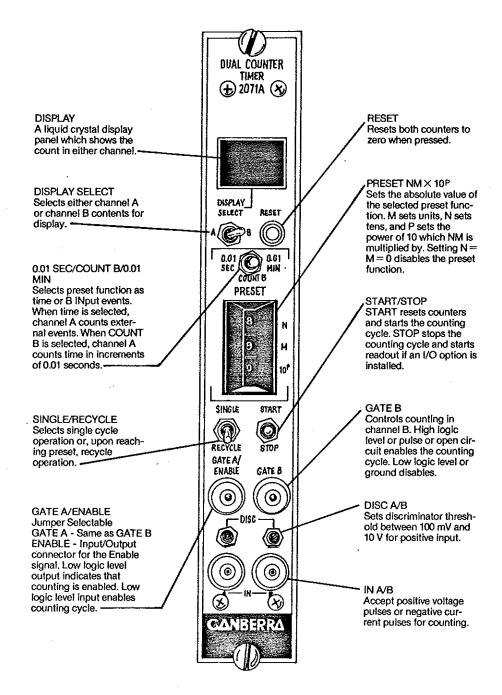

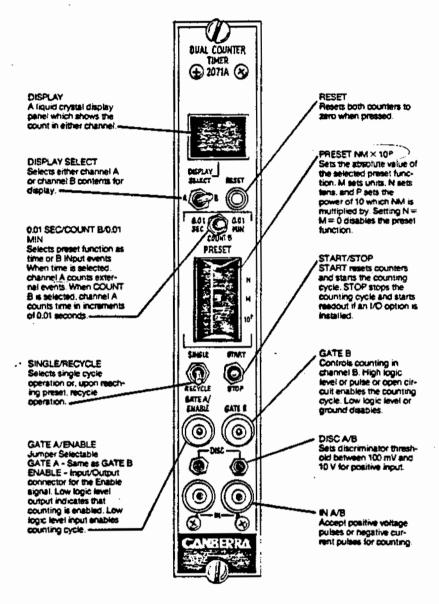

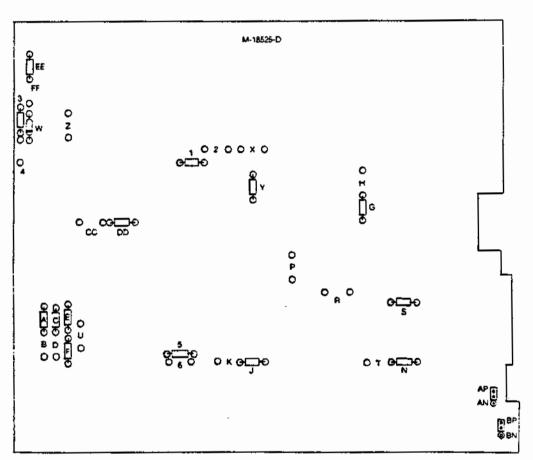

#### 3.1 FRONT PANEL

Figure 3.1 Front Panel

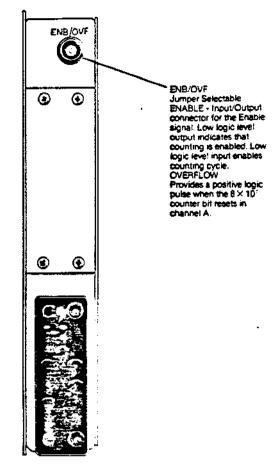

# 3.2 REAR PANEL

Figure 3.2 Rear Panel

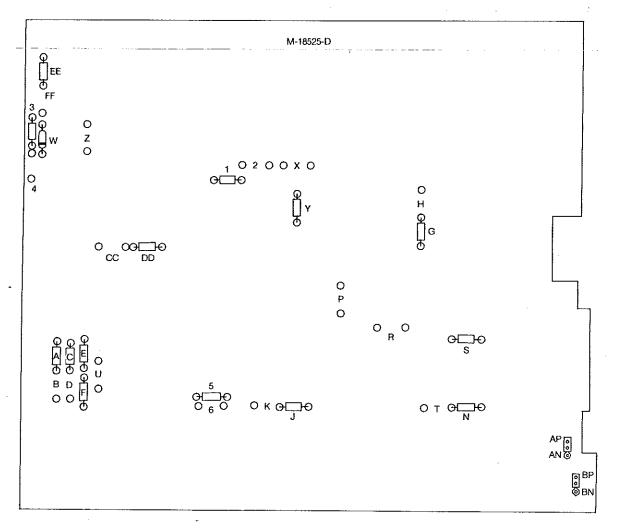

# 3.3 JUMPER OPTIONS

The Model 2071A jumpers are defined as follows:

| Jumper        | Function                                                                                         | Jumper       | Function                                                                                              |

|---------------|--------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------|

| A*<br>B       | Allows the GATE B signal to enable counter B Prevents the GATE B signal from disabling counter B | W*<br>Z      | Allows ENABLE do level to start and stop count Allows ENABLE pulse's falling edge to start count      |

| C*<br>D       | Allows the GATE A signal to enable counter A Prevents the GATE A signal from disabling           | X            | Disables LCD annunciator CNT for Dual                                                                 |

| J             | counter A                                                                                        | Y*           | Counting Enables LCD annunciator CNT                                                                  |

| E*<br>F*<br>U | Enables counting in channel A Enables counting in channel B Enables Dual Counting                | 1*<br>2      | Enables LCD annunciator SEC<br>Disables LCD annunciator SEC for Dual<br>Counting                      |

| G*<br>H       | Allows the logic to reset channel A Prevents the logic from resetting channel A                  | 3*<br>4      | Enables LCD annunciator MIN Disables LCD annunciator MIN for Dual Counting                            |

| J*<br>K       | Channel A provides OVERFLOW signal<br>Channel B provides OVERFLOW signal                         | C*           | · ·                                                                                                   |

| N*<br>T       | Enables preset select, time or counts Enables only preset time for Dual Counting                 | 5*<br>P<br>6 | Enables channel A live time gating<br>Enables channel B live time gating<br>Disables live time gating |

| R<br>S*       | Selects front panel GATE A function<br>Selects front panel ENABLE function                       | DD.<br>CC    | Selects 100 µsec recycle time<br>Selects 10 sec recycle time                                          |

<sup>\*</sup>Indicates factory set position

| Jumper                                                      | Function                                                                   |  |  |

|-------------------------------------------------------------|----------------------------------------------------------------------------|--|--|

| EE<br>FF*                                                   | Selects rear panel ENABLE function<br>Selects rear panel OVERFLOW function |  |  |

| AP*<br>AN                                                   | Selects positive A input<br>Selects negative A input                       |  |  |

| BP* Selects positive B input<br>BN Selects negative B input |                                                                            |  |  |

| *Indicates factory set position.                            |                                                                            |  |  |

- To enable the Unit as a dual counter:

move jumper F to position U

move jumper 1 to position 2

move jumper 3 to position 4

move jumper N to position T

- To disable logic reset of channel A and use manual reset only: move jumper G to position H

- To change live time gating:

move jumper 5 to position 6 to disable

move jumper 5 to position P to change from channel

A to channel B

- To disable the gate signal to channel A: move jumper C to position D

- 5. To disable the gate signal to channel B: move jumper A to position B

- To change the Overflow output from channel A to channel B: move jumper J to position K

- To change rear panel OVERFLOW to ENABLE: move jumper FF to position EE

- 8. To change front panel ENABLE to GATE A: move jumper S to position R

- To change A INput from positive to negative (NIM) input: move jumper AP to position AN

- To change B INput from positive to negative (NIM) input: move jumper BP to position BN

- To change recycle time from 10 seconds to 100 microseconds: move jumper DD to position CC

- 12. To allow the falling edge of the ENABLE input pulse to place the Unit in count: move diode W to position Z; be sure to orient the diode with the band toward the bottom of the board

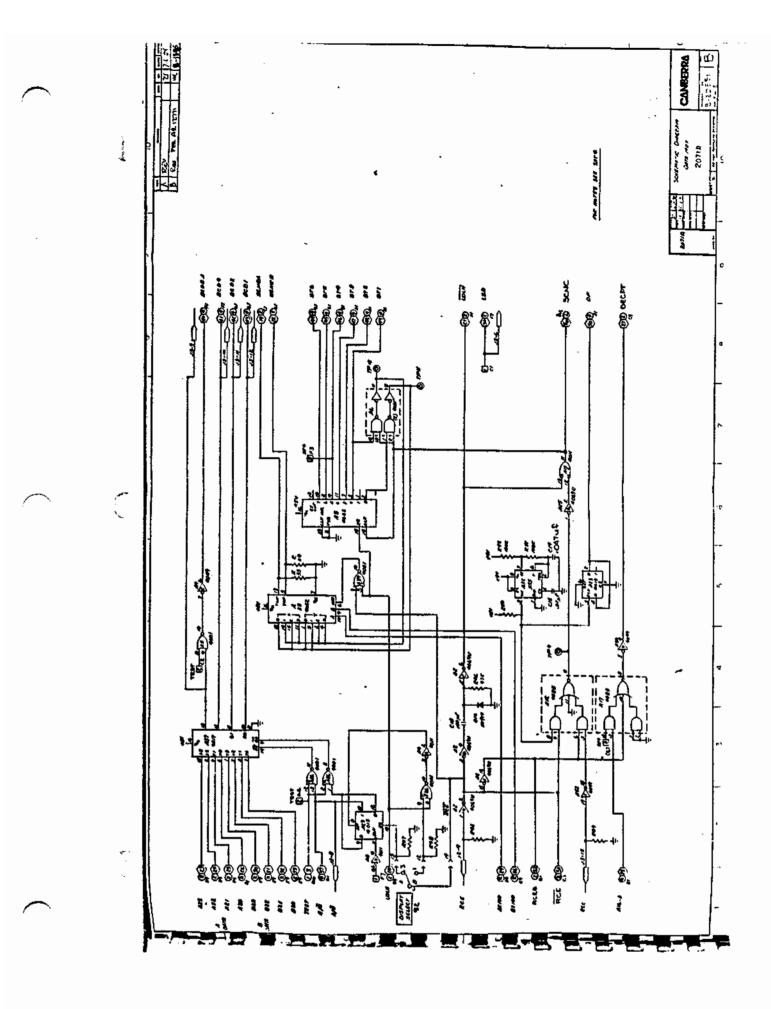

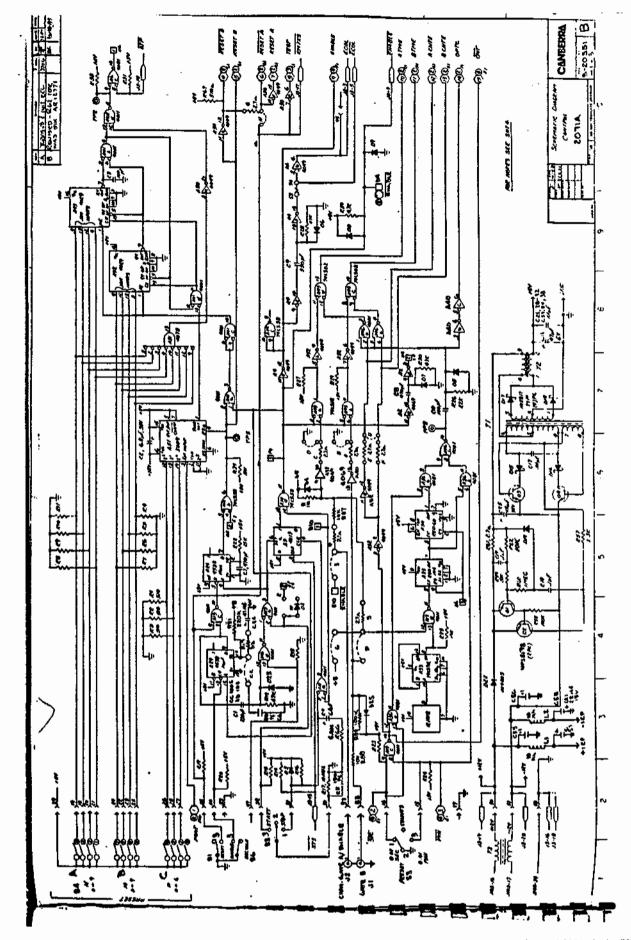

Figure 3.3 Internal Jumpers

# Section 4. Operation

The Model 2071A Dual Counter-Timer can be used as an event counter with a time preset, as a timer with a preset on a selected number of events, or, with internal jumper changes, as a dual counter preset on time. In the latter mode, time is not displayed or read out.

The unit will accept positive voltage logic pulses or negative current pulses (jumper selectable). Positive inputs are normally clamped to + 5 V and will see a nominal input impedance of 1k ohms. Negative inputs see a nominal 50 ohm input impedance.

# 4.1 DISPLAY ANNUNCIATORS

The liquid crystal display panel has, in addition to numerals to display counter contents, eight annunciators which describe the display's readout and the dynamic state of the unit.

- X100 Shows that the six most significant digits are being displayed.

- OF Shows that the displayed channel has overflowed and is counting up from zero again.

- CNT Shows that the selected channel is displaying counts. Blinks when the channel is active.

- A/B Shows which channel's contents are being displayed.

- MIN Shows that time, counted in minutes, is being displayed. Blinks when the channel is active.

- SEC Shows that time, counted in seconds, is being displayed. Blinks when active.

The eighth annunciator is a decimal point.

## 4.2 PRESET

The preset condition is set with the 0.01 SEC/COUNT B/0.01 MIN preset select switch and the three thumbwheel switches, N, M, and  $10^{\rm P}$ . Selecting 0.01 SEC or 0.01 MIN will enable the unit to be used as an event counter with the time preset in increments of 0.01 seconds or 0.01 minutes (0.6 seconds). Setting N  $\doteq$  M = 0 disables the preset function.

Selecting COUNT B will enable the unit to be used as a timer with a preset on a number of counts. - 8 gets cou

If the unit is to be changed to a dual counter, the time preset, either 0.01 seconds or 0.01 minutes, will be used but not displayed.

The thumbwheel switches are used to select the number of preset units as chosen by the preset select switch. The M switch sets the units of the preset, the N switch sets the tens, and the 10<sup>P</sup> switch sets the power-of-ten multiplier.

For instance, if the switches are set to N=1, M=0, P=3 and the preset select switch is in the 0.01 SEC position, the time preset will equal  $10\times10^3$  hundredths of a second, or 100 seconds. If the select switch is in the 0.01 MIN position, the preset will equal  $10\times10^3$  hundredths of a minute, or 100 minutes. If the select switch is in the COUNT B position, the preset will equal  $10\times10^3$  counts, or 10 000 counts.

#### 4.3 EVENT COUNTER

To use the Model 2071A as an event counter, INput A receives the external events to be counted. The 0.01 SEC/COUNT B/0.01 MIN switch must be placed in one of the time positions and the PRESET thumbwheel switches must be set for the desired time preset, as explained in section 4.2.

Pressing the START/STOP switch to START will start data accumulation. When the preset is reached, channel A will contain the total counts accumulated and channel B will contain the time during which the counts in channel A were accumulated. The time shown will equal the preset time.

To display the contents of either channel, move the DIS-PLAY SELECT switch to either A or B. Only one channel will be displayed at a time. The annunciators on the liquid crystal display will show either CNT (counts) or SEC or MIN (the selected time preset).

#### 4.4 TIME COUNTER

To use the Model 2071A as a time counter, the channel B INput receives the external events to be counted and channel A records elapsed time in increments of 0.01 seconds.

In this mode, the preset select switch is placed in COUNT B and the PRESET switches can be set to stop the counting cycle at the selected number of counts. Channel A will show the time that it took to record the preset number of events.

#### 4.5 DUAL COUNTER

By changing internal jumpers as outlined in Section 3.3.1, both channel A and channel B can count external events up to a preset time, either in 0.01 second or 0.01 minute increments as defined by the setting of the preset select switch and of the PRESET switches. In this mode, the time is not displayed or read out.

# geto courto. 4.6 SINGLE/RECYCLE

With the SINGLE/RECYCLE switch in the SINGLE position, the counter, once started, will count to preset and stop. If the switch is moved to the RECYCLE position, the counter will count to preset, pause 10 seconds or 100  $\mu$ sec as selected by jumper CC/DD, clear the counters and start counting again. The recycle mode will continue until manually stopped, by setting the SINGLE/RECYCLE switch to SINGLE and pressing STOP.

#### 4.7 RESET

At any time, even during a count cycle, pressing the RESET button will clear both counters to zero. If a counting cycle is in progress, it will resume as soon as the RESET button is released.

In the RECYCLE mode, the counters are automatically reset at start-of-count. By changing an internal jumper, channel A automatic reset can be inhibited. In this mode, channel A can be reset only by pressing the RESET button. See Section 3.3.2.

The RESET button also functions as a display check. When the button is pressed, the display will show all "eights." Therefore, holding the button down will allow the operator to verify that the display is functioning correctly.

## 4.8 SYSTEM OPERATION

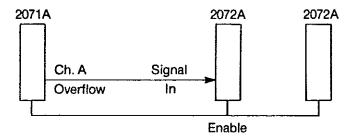

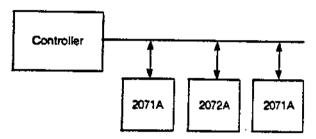

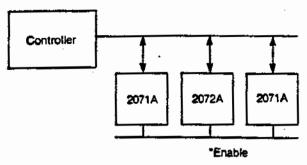

Several of the Series 2000 counting modules can be configured in a Master/Slave relationship by connecting their ENABLE connectors in parallel with 93 ohm coaxial cable (type RG-62), using female-female-female "tee" connectors between the cable segments.

When the system is connected in this way, pressing START on one unit will start all units together.

The Master unit in the system is the one whose START button has been pressed, all other units are Slaves. Note that in this mode, the Slave presets are disabled. The Master unit's preset will control the entire system. Pressing STOP on the Master will stop all units together.

Either of the input/output options may also be used to set the system up in the Master/Slave mode. See Sections 5 and 6 for details.

## 4.9 GATE A AND B

The GATE A function is available on the front panel GATE A/ENABLE connector. The factory set internal jumper must be moved from the ENABLE position to the GATE A position to allow GATE A inputs. See Section 3.3.8.

The GATE connectors accept positive logic pulses or a dc level to enable counting in either channel. Internal jumpers may be moved to disable the function for either channel or both channels. See Sections 3.3.4 and 3.3.5.

A logic high signal (+4 to + 5 V) or an open input will enable counting; a logic low signal (0 to + 0.8 V) will disable counting.

The gating signal gates the crystal-controlled time base, giving a gating time resolution of 1 µsec. Using channel A as the event counter and channel B as the timer counter, a system-busy signal may be connected to the GATEA input to disable counting and the timer for accurate dead time correction. By moving an internal jumper, Time gating can be done with GATEB or can be defeated; see Section 3.3.3.

## 4.10 ENABLE

The ENABLE function is available on both the front and rear panel. The front panel GATE A/ENABLE connector is

factory set to the ENABLE position. To select the front panel GATE A function, see Section 3.3.8. The rear panel ENB/OVF (ENABLE or OVERFLOW) connector is factory set to the OVERFLOW position. To select rear panel ENABLE function, see Section 3.3.7.

The ENABLE connector provides a logic low output (0 to 0.8 V) when the unit is enabled for counting. This output can be used to signal another unit that the Model 2071A is active. For instance, when using the Model 2071A as the Master unit in the Master/Slave System outlined in Section 4.8.

The ENABLE connector can also receive a logic low pulse to enable the Model 2071A for counting. For instance, as a Slave unit in the Master/Slave System.

To increase the Enable line's flexibility, an internal jumper (W) has been provided. If this jumper is moved to the Z position (see Section 3.3.12), the falling edge of an input pulse on the ENABLE connector will start the unit's counting cycle.

When the unit is started in this way, it is the Master unit in the system. The Enable line will be held low by this unit until its preset is reached, thus enabling all other units in the system.

If the Model 2071-02 Daisy Chain Interface is installed, it will not be necessary to use the Enable line. The Interface has all necessary signals to start and stop the unit.

If the Model 2071-01 GPIB Interface is installed, the Enable line will be used if the entire system is to start and stop at the same time. If the GPIB Controller is to address each unit separately, the Enable line will be used only if each individually addressed unit is the Master unit in separate sub-systems.

An internal jumper can be moved to change the front panel ENABLE function to GATE A. See Section 3.3.8.

## 4.11 OVERFLOW

The OVERFLOW function is available at the rear panel ENB/OVF (ENABLE or OVERFLOW) connector which is factory set to the OVERFLOW position.

The rear panel OVERFLOW connector provides a positive logic pulse every time that channel A exceeds its count capacity (10<sup>8</sup> counts). This signal can be connected to the input of another counter to extend the counting capacity of the system.

If the Model 2071A is used in the dual counter mode, the OVERFLOW signal can be connected to the B INput, instead of another counter, to extend the counting capacity of the system.

An internal jumper can be changed to allow the overflow of channel B to generate the OVERFLOW signal. See Section 3.3.6.

# Section 5. Daisy Chain Interface

The Model 2071-02 Daisy Chain Interface option provides both data input/output and system control. It is compatible with all existing Canberra Daisy Chain Systems.

The CONTROL IN and CONTROL OUT connectors present all Bus commands, with the exception of the Print clock, in parallel to all units in the system. The Print clock is presented serially to one unit at a time.

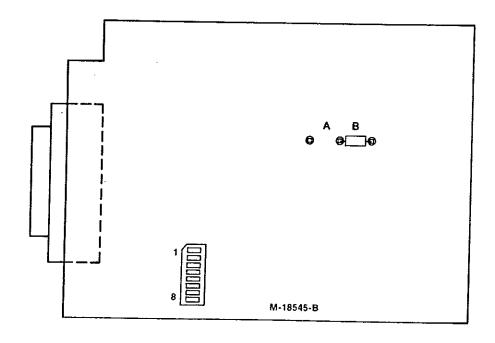

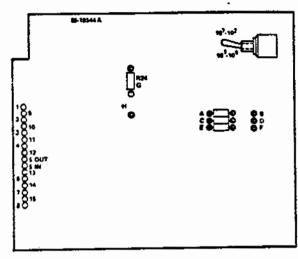

Since the Model 2071A is an eight-digit counter and the Daisy Chain System is capable of recording only six digits, a switch has been included on the Interface Board to select output of either the six most significant digits (10<sup>2</sup> – 10<sup>7</sup>) or the six least significant digits (10<sup>0</sup> – 10<sup>5</sup>). Refer to Figure 5.1 for switch location.

The nature of the data collection being performed will define which six digits to include in the data output. The unit is shipped with the switch in the six least significant digits (10° - 105) position.

#### 5.1 SYSTEM SETUP

A system of up to 50 data input modules and one scanner are connected with Model C-1404 cables. One 60 cm (two foot) cable is included with each Model 2071-02.

The CONTROL OUT connector of each unit is connected to the CONTROL IN connector of the next unit in the system. The last unit in the system is connected back to the scanner.

The system Master unit is defined as the one on which the START control is pressed. All other units are then Slave units.

When the Master unit is started, it generates a System Start command on the Daisy Chain Bus, which starts all Slave units at the same time.

When any unit reaches its preset, it stops and generates a System Stop command on the Bus. All units will stop at the same time.

In the SINGLE count mode, the system will run through one data collection cycle and stop when preset is reached.

In the RECYCLE count mode, the system will start, stop when any unit reaches its preset, pause ten seconds or 100 microseconds (jumper selectable, see Section 3.3.11), clear all counters, and start counting again.

# **5.2 PRINTING SYSTEM**

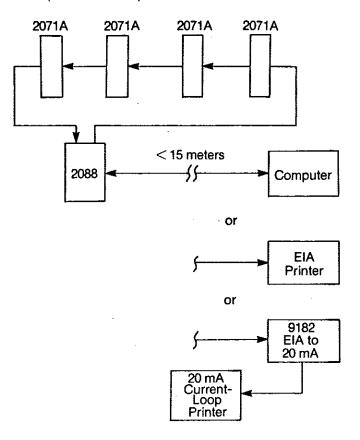

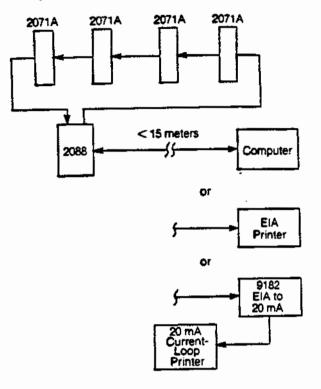

If a Model 2088 Printer Scanner (RS232), or a Model 2089 Serial Scanner-Printer is connected in the system, the data collected by each unit can be printed out. A Model 9182 EIA to 20 mA Current Loop Adaptor can be connected to the 2088 for 20 mA current loop operation.

Standard with the NIM Daisy Chain option is a read out buffer. By taking advantage of the buffer circuitry, system dead time can be reduced. In a Recycle Mode, the buffer allows the unit to be placed back into the counting mode after the data has been latched into the readout buffer. After 10 seconds or 100 microseconds, jumper selectable, counting resumes and read out begins. During the readout time, the display will not be updated, but correct counting will go on. As with most buffers, counting time must be longer than readout time.

The first unit in the system to print out will be the one connected to the Scanner's CONTROL OUT connector. The second unit to print out will be the one connected to the first unit. The last unit to print out will be the one connected to the Scanner's CONTROL IN connector.

# 5.3 COMPUTER CONTROL

The Model 2088 Printer Scanner can be used to allow a computer to control the system. Refer to the Model 2088's manual for details on computer system operation.

# 5.4 DAISY CHAIN JUMPER OPTIONS

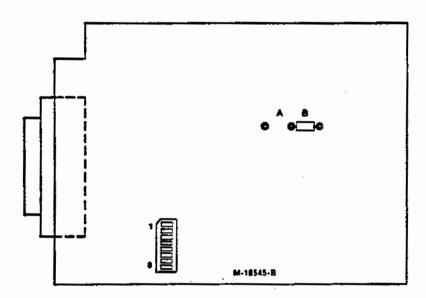

The Daisy Chain option board has four jumpers which will allow the user to tailor the option for specific applications. Three of these jumpers are 4.7k ohm resistors; the fourth is a 2.7 ohm resistor. Refer to Figure 5.1 for jumper locations.

Jumper A allows the Enable pulse's rising edge or the Model 2071A's control logic to generate the Daisy Chain Bus STOP command.

In the B position, this unit will not generate the STOP command.

Jumper Callows the Enable pulse's falling edge or the Model 2071A's control logic to generate the Daisy Chain Bus START command.

In the D position, this unit will not generate the START. command.

Jumper Eallows the Enable pulse's falling edge or the Model 2071A's control logic to generate the Daisy Chain Bus RESET command.

In the F position, this unit will not generate the RESET command.

Jumper G allows the Model 2071A's front panel RESET control to generate the Daisy Chain Bus RESET command.

In the H position, manual Reset will not generate the RESET command.

Please be aware that these jumpers do not need to be changed to make this unit a Slave unit. Slave status is normally defined by system operation.

If any or all of these jumpers were to be changed to their optional positions, this unit would be permanently defined as a Slave unit. It would never become a system Master unit until the jumpers were changed back to their usual setting.

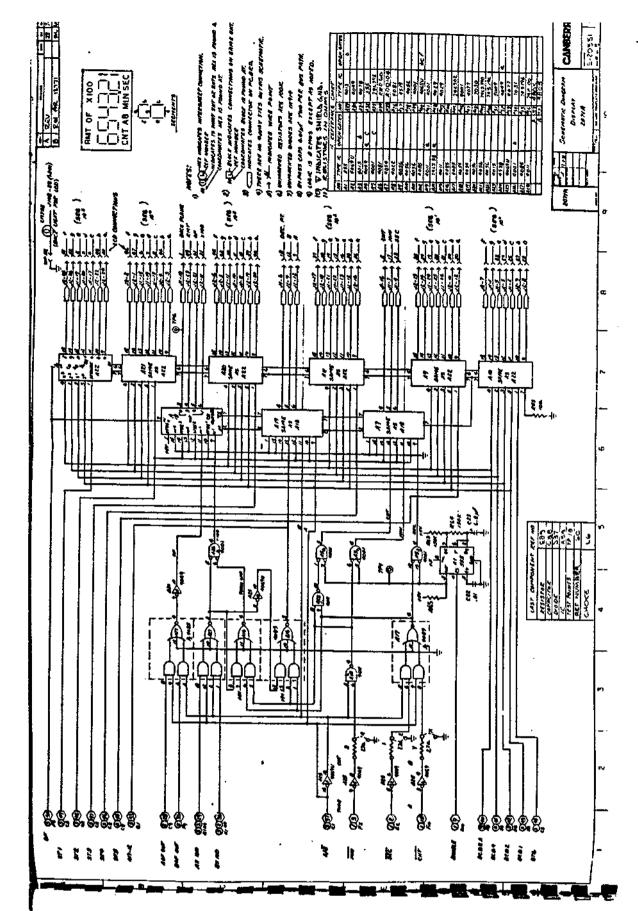

Figure 5.1

Daisy Chain Option Controls

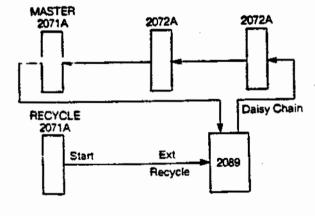

## 5.5 TYPICAL SYSTEMS

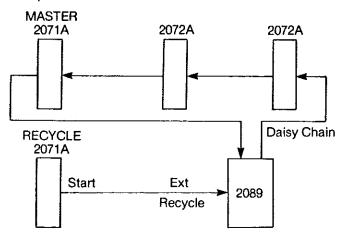

The following figures show some the possible system setups.

Multi-input system with preset time and ability to count overflow from channel A of the 2071A.

Multi-input 100 MHz Daisy Chain Printing System – preset controlled by master 2071A, recycle time controlled by 2071A. Printout from 2089 printer lists preset time and contents of 5 counters.

Note: The Model 2071A will require a factory modification (SERF) in order to operate with the Model 2089 External Recycle.

Multi-input 100 MHz Daisy Chain system with individual preset time for each counter. Slaves must reach preset before master. For this system, slaves are defined by changing the -02 option's internal jumpers (See Section 5.4).

## 5.6 USING THE MODEL 1488 SCANNER

If a Model 1488 Scanner is to be used instead of the Model 2088, the 1488 PRINT MODE switch must be set to PROMPT.

In the DELAYED mode, the HOLD command is not normally asserted until after the TTY motor-start time out, which will not allow proper data buffering.

For proper operation in the DELAYED mode, open the 1488 and look for a 10 ohm resistor soldered to points A-B (refer to schematic B-12177). Unsolder the resistor from points A-B and solder it to points A-C. This will cause prompt generation of the HOLD command on receipt of the Daisy Chain's STOP pulse.

The 1488's FORMAT switch must be set to LINE. Setting the switch to CONTINUOUS will cause incorrect data to be read out.

# 5.7 FIELD INSTALLATION OF THE DAISY CHAIN OPTION

The Daisy Chain Interface option consists of: four standoffs, four lockwashers, 12 Phillips-head screws, the rear panel control connector plate, and the interface board. To install the option, first remove both side covers, each of which is held in place by five Phillips-head screws. Then:

- If they are not already installed, install the four standoffs in the four holes in the unit's printed circuit board.

- The standoffs are to be placed on the component side of the board and fastened to the board with one lockwasher and one screw each.

- Carefully place the interface board in the unit so that the line of small circular connectors is at the rear of the board.

- With the interface board's four mounting holes lined up with the four standoffs, press the board gently down to mate the interboard connectors.

The interface board should mate smoothly with the unit's connector. If any resistance is felt, the connector is not properly aligned; lift the interface board up a little and realign the four mounting holes with the standoffs before pressing down again.

- Fasten the interface board to the standoffs with four screws, one in each corner of the interface board.

- Mount the control connector plate on the rear panel with the four remaining screws.

- Carefully align the ribbon cable's pins with the sockets of J4 at the rear of the interface board.

- Press the cable's pins firmly down into the connectors until the cable is flush with the tops of the connectors.

- Place S1, the six-digit select switch, in the desired position.

- Before replacing the side covers, check the installation for proper operation.

#### • 5.8 CONTROL IN/OUT CONNECTORS

| PIN No.              | FUNCTION                                                                 | SIGNAL DESCRIPTION                                                                                                           |

|----------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4     | BCD Data "1"<br>BCD Data "2"<br>BCD Data "4"<br>BCD Data "8"             | Logic 1 = +4V, Logic 0 = 0V<br>Logic 1 = +4V, Logic 0 = 0V<br>Logic 1 = +4V, Logic 0 = 0V<br>Logic 1 = +4V, Logic 0 = 0V     |

| 5*                   | Print Clock                                                              | +5V Pulse Train                                                                                                              |

| 6                    | System Hold                                                              | +0.5V DC Level Change                                                                                                        |

| 7                    | System Stop                                                              | +5VPulse ·                                                                                                                   |

| 8                    | System Start                                                             | +5VPulse                                                                                                                     |

| 9                    | System Reset                                                             | +5VPulse                                                                                                                     |

| 10<br>11<br>12<br>13 | Display BCD "1"<br>Display BCD "2"<br>Display BCD "4"<br>Display BCD "8" | Logic 1 = 0V. Logic 0 = +4V<br>Logic 1 = 0V. Logic 0 = +4V<br>Logic 1 = 0V. Logic 0 = +4V<br>Logic 1 = 0V. Logic 0 = +4V<br> |

| 14                   | Display Clock                                                            | Pulse Train OV                                                                                                               |

| 15                   | Ground                                                                   |                                                                                                                              |

Figure 5.2 Control in/Out Connector Wiring

## NOTES:

All data and control lines except Print Clock line (pin 5) are internally wired directly between corresponding pins of the CONTROL IN and CONTROL OUT connectors.

The Print Clock pulse train from the Data Scanner will appear on pin 5 of the CONTROL OUT connector after module has finished printing its data contents.

The signals on pins 10 through 14 are not used by this unit.

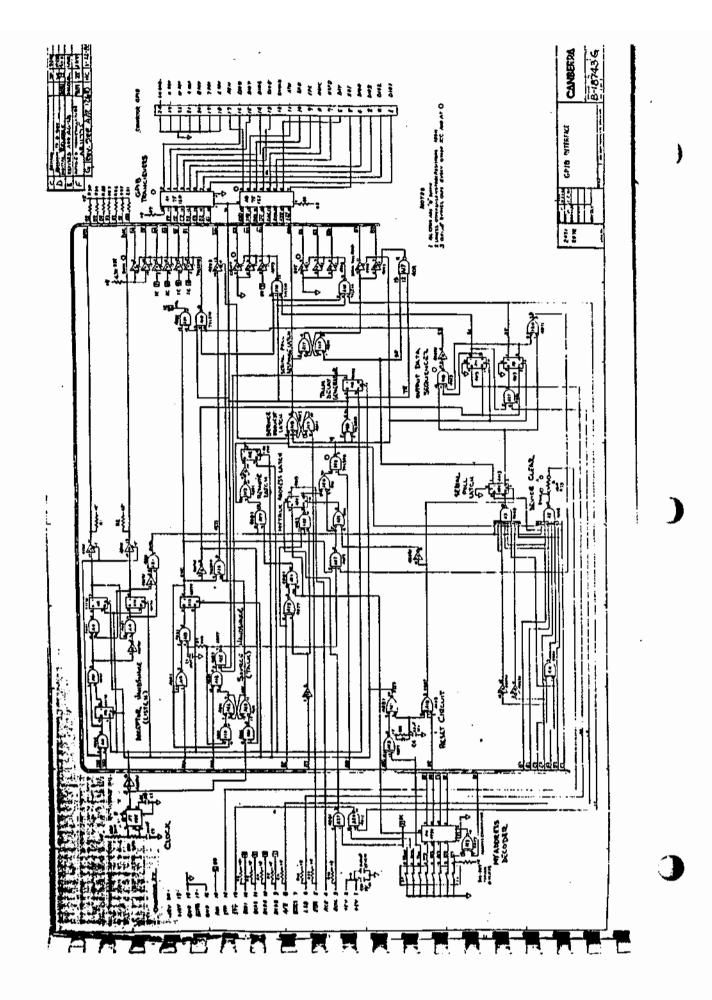

# Section 6. Interaction of Model 2071A With the GPIB

# 6.1 GENERAL DESCRIPTION OF GPIB

The General Purpose Interface Bus is a link or network by which system components communicate with each other. Each system participant performs at least one of three roles: Controller, Talker, or Listener.

A Controller manages bus communications primarily by directing or commanding which devices are to send data to other devices (Talker), or receive data from other devices (Listener) during an operational sequence. A Controller may also be interrupted or it may command specific action between devices.

The GPIB consists of 16 lines which are grouped into three sets according to function; there are 8 data lines, 3 control lines, and 5 general management lines. The 8 data lines carry ASCII characters (bit parallel) asynchronously; the control lines provide a data transfer handshake compatible with both slow and fast devices. The bus management lines allow initialization, interrupts, and special controls.

## **6.2 GPIB SWITCHES**

The eight-section DIP switch on the option board is accessible through the hole in the unit's side cover. The switches should be set to the desired positions before putting the unit in a NIM Bin. Refer to Figure 6.1.

The first five switches, counting from the top, are used to set the unit's GPIB address. Each switch is labeled with its value and with ZERO and ONE. The address is the sum of

all switches that are in the one position. An address of 31 (all switches in the ONE position) is illegal; it is reserved for the GPIB command UNTALK.

The sixth switch is labeled TALK ONLY. Refer to Section 6.3 for its uses.

The seventh switch is labeled RECYCLE. In the ON position, the unit will clear after readout and start counting again. In the OFF position, the unit is in the single cycle mode.

The eighth switch is labeled FF/CR. In the FF position, the message unit delimiter is sent out as an ASCII Form Feed. In the CR position, the delimiter is sent out as a Carriage Return. The choice of delimiter depends on the peripheral device being used.

# 6.3 SYSTEMS WITHOUT A CONTROLLER

The Model 2071A can operate in the Talk Only ON mode, which is used when data from a single module is to be passed directly to a single peripheral Listener device, such as a GPIB Printer. In this case a Controller is not required, but the printer must be in the Listen mode. Not all GPIB printers will operate in this mode.

In Talk Only ON mode, the 2071A will transmit its data to the listener as soon as 2071A data acquisition is stopped (by STOP or reaching Preset).

Figure 6.1

GPIB Option Controls

# 6.4 INTERACTION WITH A CONTROLLER

Communication with a Controller requires 2071-01's TALK ONLY switch to be off. The Controller must assert REN (Remote Enable) during the entire communication. If REN is disabled, the 2071-01 will be reset. The first requisite is for the Controller to cause the 2071A to be placed in its Remote mode. It does this by transmitting on the GPIB, MTA, (My Talk Address) or MLA (My Listen Address), with ATN (Attention) asserted. MTA or MLA must agree with the five-bit address setting on the 2071A. The following MTA or MLA would be sent if the address setting was 5.

|     | D107 | D106 | D105 | DI04 | DI03 | D102 | DI01 |

|-----|------|------|------|------|------|------|------|

| MTA | 1    |      |      |      |      | 0    |      |

| MLA | 0    | 1    | 0    | 0    | 1    | 0    | 1    |

If MTA is sent, the unit goes into its Remote mode and transmits all of its data (19 bytes). If MLA is sent, the 2071A does not respond further than placing itself into the Remote mode. Once in the Remote mode, the unit is able to generate an SRQ (Service Request) or respond to a DC (Device Clear). Disabling REN causes the 2071A to leave the Remote mode.

A typical counting sequence would begin with the operator pressing START on a 2071A that is connected to the GPIB. After reaching a preset, the 2071A will generate SRQ. The Controller would then, via a Serial Poll, determine the device requiring readout. Then send the proper MTA to read the data by way of a Read Data Interchange (Section 7.10). If the module is in the Recycle mode (switch on GPIB interface set to Recycle), the counters will be reset after readout and the counting cycle will begin again.

Note that there are two Recycle switches, one on the unit's front panel, and one on the GPIB interface card. The front panel switch allows the user 10 seconds to manually copy the display (or just view it) between cycles. When the 2071A is connected to the GPIB, the front panel switch is normally set to Single, and the GPIB interface switch set to Recycle. The recycle time will now depend on the devices on the bus with which the module must interact.

The time required to read data from a Model 2071A is determined by the sum of the response times of the Computer/Controller and 2071A. The 2071A responds to each query or handshake request within seven microseconds. This means the 2071A requires a maximum of 14 microseconds for each byte outputted. The 19-byte readout consumes 266 microseconds of 2071A synchronizing time. A readout to one Controller was measured at 12.5 milliseconds. This equates to 644 microseconds to accept data and generate handshake responses per byte, or a ratio of Controller to 2071A of 46 to 1. It is apparent that the Controller is the major contributor to readout time.

Some additional capabilities are:

# a. Controller Start

Since modules are independent, the Controller can start each module by performing a READ DATA Interchange (see Section 7.10). With a counter stopped and in a GPIB recycle mode, the completion of a READ DATA Interchange will cause it to clear and start counting. The controller can individually address each module for this sequence.

## b. Controller Stop

The Controller can send a Universal DEVICE CLEAR out on the bus, and all modules will stop counting. Individual modules cannot be addressed with this command, and it will not clear the modules, only stop them. If internal jumper B is moved to A, the module will ignore the DEVICE CLEAR command (see Figure 6.1).

# c. Read Out While Counting

The Controller can read out each individual 2071A or 2072A while it is counting by performing a READ DATA Interchange (see Section 7.10). In this case the module will be read out and will not clear, but continue counting. A point to remember here is that a module will clear itself only if it is restarted by:

- 1. A manual front panel START.

- 2. A manual front panel RESET.

- 3. An ENABLE signal input.

- Being in a front panel RECYCLE mode and stopped either by reaching preset or by receiving a Device Clear from the Controller.

- Being in a GPIB Recycle mode, stopped by reaching preset or receiving a Device Clear from the Controller, then read out by a READ DATA Interchange.

# 6.5 THREE COMMON METHODS OF OPERATION:

# A. Controller completely controls modules.

## Sequence:

- Controller performs READ DATA Interchange to start the modules. Each one must be addressed individually by the Controller. Thus, in this case, a simultaneous start is not possible. Data read out the first time is information left by previous operations.

- Controller sends a DEVICE CLEAR, when desired, to stop all counters. Individual addressing is not possible with this command. All counters will simultaneously stop.

- Controller again addresses each module with a READ DATA Interchange. Since they are in the Recycle mode (they would not have started in the first step if they weren't) each one clears, and restarts after reading out.

# B. Controller acts only as a readout device.

#### Sequence:

- 1. ENABLE input/outputs on all modules are connected.

- 2. The START switch on one 2071A is pushed (this defines it as the Master).

- 3. All modules are stopped when the master reaches its preset.

- Each module sends a SERVICE REQUEST when it stops if it was first commanded to REMOTE by the Controller.

- The Controller addresses each module and reads it out.

- 6. If the Master is in the front panel RECYCLE mode, upon being read out it will enable the system to start counting again. All modules will have been cleared by the leading edge of the ENABLE signal. Normally the Master would be interrogated last so that it does not start the system until all other units have been read out.

- C. Controller initiates simultaneous start by addressing the master module.

# Sequence:

- 1. ENABLE input/outputs on all modules are connected.

- Controller addresses first 2071A and reads it out. This

defines it as the Master. Because it is in the GPIB

Recycle mode it reads out, clears, and starts collecting. Since the ENABLE ports are connected, the other

2071A and 2072A modules clear and simultaneously

start collecting. The Single/Recycle switch on each of

their GPIB interface cards and front panel must be in

the SINGLE mode.

3. When the preset on the Master 2071A is reached, it stops all modules, and each one generates a service request on the GPIB Bus. The Controller now interrogates each module. It should address the Master 2071A last, since this module is in the recycle mode and would start the system again once it is read out.

The modules on which the START switch is not pushed will ignore their presets and be controlled by the ENABLE signal. The Master module is defined as the module that has been started first, either manually or by being addressed from the Controller. Its preset will determine the presets for all other 2071As and 2072As.

# 6.6 FIELD INSTALLATION OF THE GPIB OPTION

The GPIB Interface option consists of: four standoffs, four lockwashers, 12 Phillips-head screws, a rear panel cover plate marked J102, and the interface board.

To install the option, first remove both side covers, each of which is held in place by five Phillips-head screws. Then:

- If they are not already installed, install the four standoffs in the four holes in the unit's printed circuit board.

- The standoffs are to be placed on the component side of the board and fastened to the board with one lockwasher and one screw each.

- Carefully place the interface board in the unit so that the large connector at the rear of the board is flush with the rear panel.

- With the interface board's four mounting holes lined up with the four standoffs, press the board gently down to mate the interboard connectors.

The interface board should mate smoothly with the unit's connector. If any resistance is felt, the connector is not properly aligned; lift the interface up a little and realign the four mounting holes with the standoffs before pressing down again.

- 5. Fasten the interface board to the standoffs with four screws, one in each corner of the interface board.

- Place the J102 cover plate on the unit's rear panel and fasten it in place with the remaining four screws.

- 7. Before replacing the side covers, check the installation for proper operation.

# 1. INTRODUCTION

The Canberra Model 207x-03 EIA Interface provides readout, start, and stop of the Models 2071, 2071A, 2072, and 2072A counters by an EIA-compatible printer, terminal, or computer.

Multiple 207x modules, each with an 207x-03 option, can be chained together. This allows the terminal or computer to control or read out modules either individually or all at once, making possible multiple Master/Slave operation or multiplexed independent experiments.

# 1.1. Mode Selection

A cutout on the 2071A or 2072A's side panel provides access to DIP switches for:

- EIA Single/Recycle Operation

- Enable/Disable generation of Form Feeds, Line Feeds, Spaces and Carriage Returns in readout

- Select Baud Rate

- Select Operating Mode: Single Unit or Chain Mode

- · Select Unit Status (chain mode): Master or Slave

# 1.2. Control Commands

Commands from a terminal or computer include:

- •Start, Stop, and Reset of the module.

- Readout of module when stopped, during counting cycle, or during storage to the 207x-03's internal buffer for future readout.

- Change readout format: leading zero suppression, CR after each number, variable pause after each character and/or CR, and delayed response to readout command.

- Address one module or all modules on EIA chain.

- Select XON/XOFF software handshake.

# 2. INTERNAL CONTROLS

The ten-section DIP switch on the option board is accessible through the opening in the unit's left side cover.

Table 2.1 DIP Switch Functions

| SWITCH | <u>FUNCTION</u>        |

|--------|------------------------|

| SW1    | RECYCLE/SINGLE CYCLE   |

| SW2    | FF :                   |

| SW3    | LF                     |

| SW4    | CR                     |

| SW5    | SP.                    |

| SW6    | BAUD 2:                |

| SW7    | BAUD 1 : See Table 2.2 |

| SW8    | BAUD 0:                |

| SW9    | ECHO/MASTER ENABLE     |

| SW10   | EIA CHAIN/SINGLE UNIT  |

2.1. Switch Setup

The following list describes the function of each of the ten DIP switches. An asterisk (\*) indicates the factory setting for each switch.

#### SW1

OFF\* Selects Single Cycle mode. When unit stops counting it will read out, but not start up again unless the Front Panel SINGLE/RECYCLE is in the RECYCLE position. ON – Selects Recycle mode. When unit stops counting, it

will read out, clear, and start counting. Front Panel RECYCLE cannot be selected while in this mode.

#### SW<sub>2</sub>

OFF\* No Form feeds generated during readout. ON – Form feeds generated during readout.

#### SW3

ON\* Line feeds generated during readout. OFF - No Line feeds generated during readout.

#### SW4

ON\* Carriage Returns generated during readout. OFF - No Carriage Returns generated during readout.

#### **SW5**

ON\* Spaces generated during readout. OFF - No Spaces generated during readout.

# SW6-SW8

Switches SW6-SW8 set the baud rate (Table 2.2)

Table 2.2 Baud Rate Settings

| Baud  | SW6 | <u>SW7</u> | <u>SW8</u> |

|-------|-----|------------|------------|

| 19200 | ON  | ON         | ON         |

| 9600  | ON  | ON         | OFF        |

| 4800  | ON  | OFF        | ON         |

| 2400  | ON  | OFF        | OFF        |

| 1200  | OFF | ON         | ON         |

| 600  | OFF | ON  | OFF |

|------|-----|-----|-----|

| 300* | OFF | OFF | ON  |

| 150  | OFF | OFF | OFF |

# SW9

OFF\* In EIA Chain mode (SW10 ON) unit not a master. In Single Mode, characters sent to the 207x-03 are not echoed

ON – In EIA Chain mode, unit is master (select SW9 ON in Unit # 1 only). In Single Mode, characters sent to the 207x-03 board from the computer are echoed back to the computer.

# SW10

OFF\* Selects Single Unit mode of operation, no chain

operation allowed.

ON – Selects EIA Chain mode of operation, all units in chain must have this switch ON.

# 3. OPERATION

# **6.7 CONNECTOR**

A 24-pin standard GPIB connector (J102) is mounted on the rear panel. It carries the following signals:

| Pin                                                                                                                                 | Signal                                                                                                                                                                      | Description                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24 | DIO1 DIO2 DIO3 DIO4 EOI DAV NRFD NDAC IFC SRQ ATN Shield DIO5 DIO6 DIO7 DIO8 REN Twisted pair | r with pin 7<br>r with pin 8<br>r with pin 9<br>r with pin 10<br>r with pin 11 |

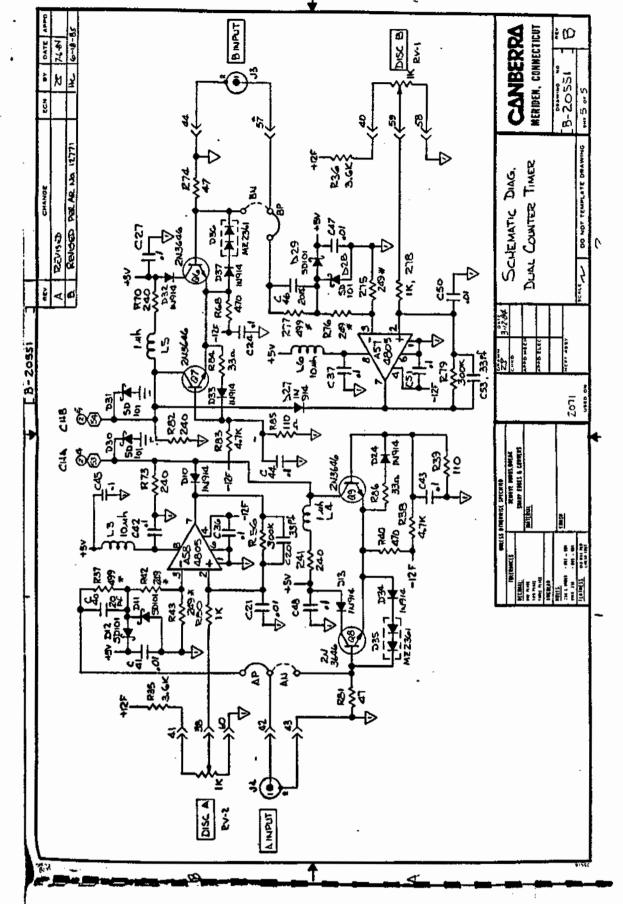

# Figure 6.2 GPIB Connector Wiring

All GPIB signals are negative-true TTL compatible:

True = 0 to 0.4 V; False = 2.5 to 5 V.

# Section 7. Theory of Operation

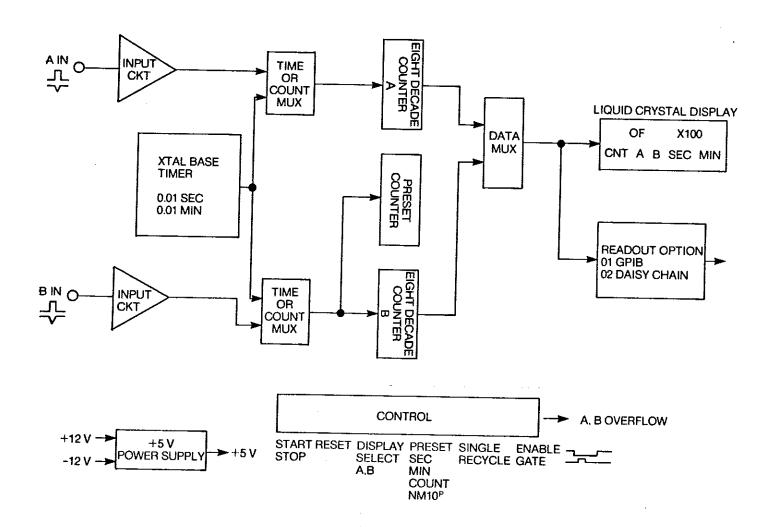

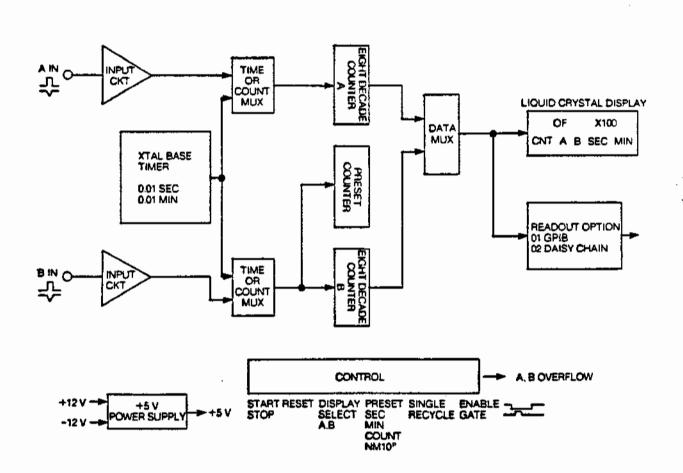

The Model 2071A includes two identical eight-decade counter channels, a crystal-based time generator, an eight-decade preset counter, a six-decade liquid crystal display, optional readout to a Canberra Daisy Chain Scanner or to a GPIB (IEEE 488) system, suitable control logic, and the power supply.

# 7.1 EIGHT DECADE COUNTING CHANNEL

Each of the identical counting channels has an input circuit which accepts positive voltage or negative current logic pulses on the same input connector (jumper selectable). Negative current-pulses see a 50 ohm impedance while the positive voltage-pulses see a nominal 1k ohm impedance.

With the A input jumper in the AP position, positive voltage signals are fed to the inverting input (pin 3) of comparator A58. A voltage divider consisting of R37, R42, and R43 along with clamping diodes D11 and D12 protect A58 from positive or negative over-voltages. When the positive input signal exceeds the threshold level set at A56-3 by R35 and front panel DISC A (RV2), A58-7 goes from 5 by fo ground. This signal is fed through D10 to A56. Double counting with slow rise times is prevented by the feedback network consisting of R56, C20, and C21.

With the A Input jumper in the AN position, negative current input pulses are received by the 47 ohm terminating resistor R81 which develops a voltage drop fed to the base of Q8. When the voltage drop exceeds the threshold voltage set on Q9 base by R38 and R39, Q8 turns off and Q9 turns on. This brings Q9 collector and A56 input from  $\approx$  2.5 V to ground. Components D35, D34, R86 and D24 protect Q8 and Q9 from positive or negative overvoltages.

Operation of Channel B is identical to that of channel A.

Multiplexing counts or time ticks to the counter is carried out by A56 (74F00). Two gates are used by each counting channel. The first decade, which is required to count at 100 MHz, is a 74S196. The second, counting at 10 MHz maximum, is half of a 74LS390. The remaining six decades reside in a LS7031. The 7031 contains six counting decades, latches, and multiplexing logic to read out the six decades plus the data of the two decades ahead. Additionally, it contains logic to recognize leading zeroes and overflow conditions. Thus, in a simple 40-pin IC, a single 14-pin IC, plus half of 16-pin IC, we have an eight decade counter with readout multiplexing.

A counting sequence is initiated with a reset pulse setting all eight decades to zero. Either external events or time ticks are gated to the clock input of the 74S196. The eight bit of the 74S196 clocks the 74LS390, and in turn the eight bit of the 74LS390 clocks the 7031 input decade.

To read the contents for display or read out the counter, data is transferred to latches within the 7031 by means of the Load Latch pulse. The next part of the sequence is to generate a Scan Reset which places the most significant digit (in BCD format) on the four data output lines. As each succeeding digit is required, a Scan Clock pulse is applied to the 7031 which places the next less significant digit on the data output lines. Because the display consists of six digits and the counter capacity is eight, at the time the 10<sup>5</sup> counter decade 8 bit resets, A29 is toggled to the one state.

The signal out of the 7031 "D6" is this bit  $(8\times10^5)$ , and the output of A29 is called "X100". X100 true causes the X100 display annunciator to turn on and causes a two-digit shift in the data displayed.

The BCD data out of the 7031 is immediately passed through A53, a quad Exclusive-NOR gate. Its function is to either invert or not invert the data. The internal leading zero logic determines this and Blank Out is the signal. The utilization of this function is by the LCD display drivers. When they see a binary 15 they respond by displaying a blank. A BCD zero out of the 7031, if it is an insignificant (leading) zero, is then coverted to binary 15 by inversion and is blanked on the display.

Figure 7.1

Model 2071A Block Diagram

# 7.2 CRYSTAL BASED TIME GENERATOR

The required 0.01 second and 0.01 minute time ticks originate from a 12 MHz crystal oscillator circuit (OSC1). This frequency is divided by 12 in A33. The resulting one MHz may be gated (jumper selected) by the GATE signal as it passes through A13. This provides the unit a capability for measuring Live Time with a one microsecond resolution. The one MHz is then applied to a prescaler (A35) which provides a divide by 104 and gives a 0.01 sec output. Dividing the 0.01 sec by 60 (A34) provides the 0.01 min output. The selected time signal may be seen at TP8.

#### 7.3 PRESET COUNTER

The eight-decade preset counter with three-digit control consists of a six-decade programmable prescaler plus a two decade down-counter. The three digit thumbwheel swich, labeled NM10P provides the eight decades of control. The P switch, with range zero through six, gives direct control over the prescaler (A51). A setting of zero means the input pulses are passed directly through. A setting of six results in the input prescaled (divided) by 106. The N and M switches provide the start number for the two decade down-counter (A42, A43). In operation, the N and M decades are loaded with their preset numbers while the unit is not enabled to count. Once enabled, the N and M switches have no control; presets N and M will not be changed at any time, doing so during Enable True is not recommended. Setting both N and M to zero satisfies an eight-input NOR gate (A31) which disables the borrow from the two down counters, which normally occurs when preset is reached. Therefore, N = M = 0 turns the preset function off. It should be noted also that the contents of A51, A42, and A43 are not available for readout.

# 7.4 SIX DECADE LIQUID CRYSTAL DISPLAY

The six-decade liquid crystal display (LCD) has each digit driven by a seven-segment LCD driver IC. With this scheme all digits are driven in parallel (that is, all ON segments are turned on at the same time). The requirement to turn a segment on is that an rms voltage be applied between the backplane and particular segment that is greater than the ON threshold for the LCD. This is accomplished by applying a square wave to the backplane and another to each segment. In-phase square waves result in zero rms (OFF) and 180° out-of-phase results in an rms of 5 V (ON). The type 4056 driver consists of a four-bit latch, a seven-segment decoder and an exclusive-OR array to select the proper phase of the signal applied to each segment.

The same clock (A32) used to strobe the data from the 7031s also provides the approximately 25 Hz square-wave display clock. In addition to the six digits, any of eight annunciators can be shown to describe the data being displayed. "CNT" is displayed when counts from an external source are selected for display. When time is selected, the annunciator "SEC" (seconds) or "MIN" (minutes) will be on. Seconds or Minutes are displayed with a maximum resolution of 0.01 units, therefore a decimal point annunciator is employed, further describing the information displayed. Because the data source may be from the A channel or B channel, A and B annunciators are provided. When the magnitude of the number exceeds six digits (105-1) a X100

annunciator is enabled and the displayed data is shifted so that the display is 107 to 102, the six most significant digits. It should be noted that loosing two digits means a display error ranging from 0.01% to zero. GPIB readout data includes the full eight digits. The remaining annunciator "OF" (overflow) turns on when the counter reaches 108 counts and remains on until data is reset.

The annunciators are driven by three 4054 four-signal segment drivers. These include latches and exclusive-OR arrays to develop the display-signal phasing required. Combinatorial logic consisting of gates A5, A15, A16, A17, A25, A26, A27, A28 determine which annunciators are on. Additionally A1, a slow oscillator, causes CNT, MIN, or SEC to blink during active counting.

The circuit to obtain data from each of the 7031s is essentially the same for readout or display. The selection of data from either the A channel or B channel is accomplished by multiplexer A37, whose data selection is controlled by the front panel Display Select switch and A23. A 23 is needed so that the data can be changed remotely in readout, allowing readout of both channels.

An oscillator (A32) running at about 50 Hz (divided by the other half of A23, to 25 Hz for the display clock) supplies the 7031 scan clock and an 8-stage Johnson counter (A8). The eight outputs of the Johnson counter are synchronous with the 7031 Digit Strobes and hence, the 7031 output data. The Johnson counter outputs strobe the data into the display LCD drivers. Also the first (TP11) or third (TP12) strobe generates a scan reset. This maintains synchronization and generates the X100 display data shift. Scan reset with the first strobe allows a display of 105 → 100. Scan reset with the third strobe allows a display of X100 or 107-102. This is accomplished by sending the first and third strobe pulses through A38, a dual multiplexer controlled by X100 signals from the A counter and B counter. In readout, the A32 oscillator is replaced by read clocks from the readout option. This is accomplished by half of A12,

# 7.5 CONTROL

The block diagram area labeled Control provides interactive control with all the blocks on the diagram. The prime control capabilities are to place the unit into the count enabled mode, determine which counter counts external events, and various jumper controlled options.

The signal ENABLE, brought to a front panel or rear panel BNC connector, is the count enable function. A low is the true state indicating counting is enabled. This is a bidirectional signal path which allows an external master unit to enable both channels for an externally determined time. The preset logic has no function in this slave mode of operation. The logic sequences in this mode are that once the ENABLE level has been pulled low by the master, a 10 microsecond reset pulse is generated (TP5) and sent to both A and B channels. This means a 10 microsecond dead time is incurred at the beginning of a measurement period. The timer logic, however, is not affected by this; thus time is measured from the beginning edge of ENABLE with only a two to three microsecond propagation delay error.

A Model 2071A may be either a master or slave with no jumper or control changes. Determination of master or slave status is dependent on whether or not the START switch has been pressed. The START switch causes one-half of A3 to be set. It, in turn, drives the ENABLE line low through A14-11. At this point any other units receiving the ENABLE signal are enabled to count as slaves. After the 10 microsecond reset period has elapsed, both counting channels and the preset channel are allowed to accumulate data.

The presence of a Daisy Chain option results in a slightly different concept of master and slave. This option provides interconnected START, STOP, and RESET signals to all units in the system. The preset control N, M,  $10^p$  must be set to N = M = 0 for a unit to operate as a slave. The ENABLE signal is not used (not connected between units). In this case the unit whose START switch was pressed (not necessarily the master unit) causes the Daisy Chain START pulse to toggle A3 to the one state via signal ST5 in each module.

Termination of counting occurs when the master reaches preset. This occurs on the simultaneous occurrence of borrow from both preset down-counters (A42 and A43), seen as a negative pulse at TP2. Pressing the STOP switch also terminates counting. The master unit then generates the STOP signal to the remainder of the system, terminating the experiment.

Determination of whether a channel counts time or external events is normally based on the preset selector, 0.01 SEC/COUNT/0.01 MIN, position. A preset of either time position results in that time interval being accumulated in channel B. Channel A will then accumulate external events through the A INput connector. Selecting a preset of counts causes external events through the B INput connector to be accumulated in channel B. The A channel will accumulate 0.01 second time intervals.