## Model 1510 Integrated Signal Processor

3/95

User's Manual

Copyright 1995, Canberra Industries, Inc. All rights reserved.

This manual contains proprietary information; no part of it may be reproduced or used in any form or by any means – graphic, electronic, or mechanical, including photocopying, recording, or information storage and retrieval systems – without the written permission of Canberra Industries.

The information in this manual describes the product as accurately as possible, but is subject to change without notice.

Printed in the United States of America.

Canberra Industries, Inc., 800 Research Parkway, Meriden, CT 06450 Telephone: (203) 238-2351 FAX: (203) 235-1347

## **Table of Contents**

|    | Introduction  1.1 High Voltage Bias Supply  1.2 Spectroscopy Amplifier  1.3 Pile-up Rejection/Live-time Correction  1.4 ADC                                                                                                                                                                                                                                           | 1                                                  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 2. | Applications, Hardware and Accessories                                                                                                                                                                                                                                                                                                                                | 4                                                  |

| 3. | Setup                                                                                                                                                                                                                                                                                                                                                                 | . 7                                                |

| 4. | System Integration and Connections                                                                                                                                                                                                                                                                                                                                    | . 9<br>. 9                                         |

| 5, | Operation 5.1 Pre Turn-On 5.2 Turn On 5.2 Turn On 5.3 Amplifier Setup 5.4 Pole/Zero (P/Z) Adjustment 5.5 ADC Setup 5.6 Spectroscopy Operation 5.7 PUR/LTC Operation 5.8 Performance Adjustments 5.9 Incoming Count Rate (ICR) 5.10 Pileup Rejection With a Live Source 5.11 Live Time Correction With a Live Source 5.12 ADC Gate 5.13 Sampled Voltage Analysis (SVA) | 12<br>13<br>13<br>14<br>14                         |

| 6. | Circuit Description  6.1 Amplifier                                                                                                                                                                                                                                                                                                                                    | 20<br>20<br>20<br>20<br>21<br>21<br>22<br>22<br>23 |

| A. | Specifications                                                                                                                                                                                                                                                                                                                                                        | <b>24</b>                                          |

|    | A.1.1 Inputs                       |    |

|----|------------------------------------|----|

|    | A.1.2 Outputs                      | 24 |

|    | A.1.3 Front Panel Controls         | 24 |

|    | A.1.4 Internal Controls            | 25 |

|    | A.1.5 Performance                  | 25 |

|    | A.2 100 MHz ADC                    | 26 |

|    | A.2.1 Inputs                       |    |

|    | A.2.2 Outputs                      | 26 |

|    | A.2.3 Front Panel Controls         | 26 |

|    | A.2.4 Internal Controls            |    |

|    | A.2.5 Indicators                   |    |

|    | A.2.6 Performance                  |    |

|    | A.3 High Voltage Bias Supply       |    |

|    | A.3.1 Inputs                       |    |

|    | A.3.2 Outputs                      |    |

|    |                                    |    |

|    | A.3.3 Controls                     | 21 |

|    | A.3.4 Indicators                   |    |

|    | A.3.5 Performance                  |    |

|    | A.4 System Rear Panel Connectors   |    |

|    | A.5 Standard Accessories           |    |

|    | A.6 Interface Cables               |    |

|    | A.7 Optional Cable                 |    |

|    | A.8 Physical                       | 29 |

| 0  | High Voltage Polarity/Range Module | 32 |

| ٥. | B.1 Polarity                       |    |

|    |                                    |    |

|    | B.2 Voltage Range                  | JJ |

| C. | Internal Controls and Connectors   | 34 |

|    | C.1 Operating Voltage Selection    |    |

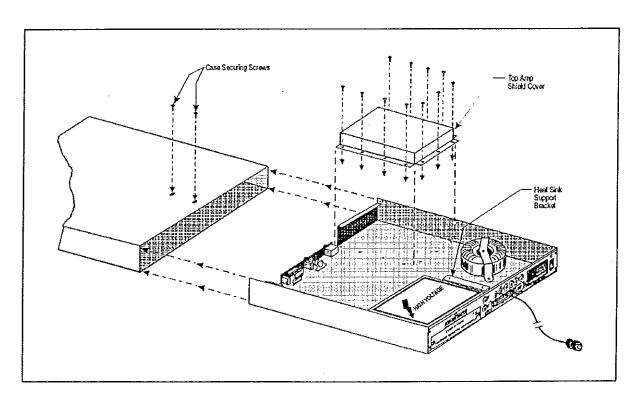

|    | C.2 Case Removal                   |    |

|    | C.3 Amplifier Top Shield Removal   |    |

|    | C.4 Amplifier Internal Jumpers     |    |

|    | C.4.1 Z-out                        | 37 |

|    | C.4.2 JA, JB, SYM-ASYM             |    |

|    | C.4.3 J5, INH-INH/                 |    |

|    | C.5 ADC Internal Jumpers           | _  |

|    | C.5.1 J2, Dead Time Polarity       |    |

|    | C.5.1 JZ, Dead Tille Folding       | 27 |

|    | C.5.2 J8, Enable Data              |    |

|    | C.5.3 J9, Data Buffer              |    |

|    | C.5.4 J10, Data Accepted           | 38 |

|    | C.5.5 J11, Data Ready              |    |

|    | C.5.6 J12, PHA/SVA                 |    |

|    | C.5.7 J13, Coinc/Anti              | 39 |

|    | C.5.8 J14, Enable Converter        |    |

|    | C.6 ADC Setup Diagrams             | 39 |

| _  | Performance Adjustments            | 40 |

| J. | ·                                  |    |

|    | D.1 Amplifier Pole/Zero (P/Z)      | 40 |

| D.2 Amplifier Shaping Selection                                                                                                                                                                                 | . 42<br>. 43                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| E. System Considerations with High Resolution Detectors E.1 System Design Considerations                                                                                                                        | . 45                                 |

| F. ADC Interfacing and Data Transfer F.1 ADC Data Transfer F.2 Dependent ADC Applications F.3 The Invalid Flag F.3.1 Invalid Flag Conditions F.4 Dead Time F.5 Enable Converter F.6 J102 Data Connector Signals | . 48<br>. 50<br>. 50<br>. 50<br>. 51 |

| G. Rack Mount Hardware                                                                                                                                                                                          |                                      |

| H. ADC/MCA Interface Cables H.1 Hardware Installation H.2 C1547-4 ADC/MCA Interface Cable H.3 C1545A ADC/MCA Interface Cable H.4 C1556 ADC/MCA Interface Cable H.5 C1554 ADC/AIM Interface Cable                | 54<br>55<br>55<br>56                 |

| List of Figures                                                                                                                                                                                                 |                                      |

| Figure 2.1 A Typical Nal(Tl) System                                                                                                                                                                             | . 6<br>10<br>11<br>12<br>17<br>30    |

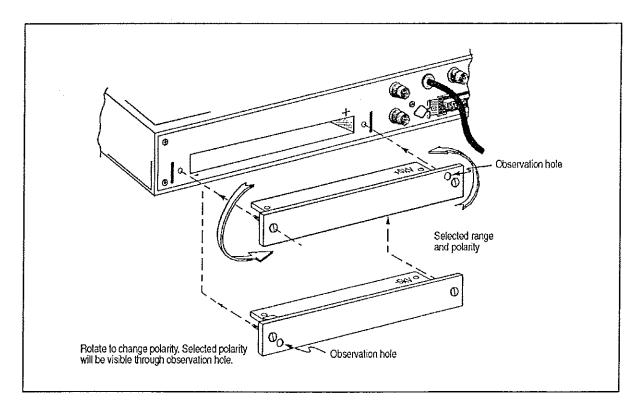

| Figure B.1 HVPS Programming Module Removal and Installation                                                                                                                                                     | 32                                   |

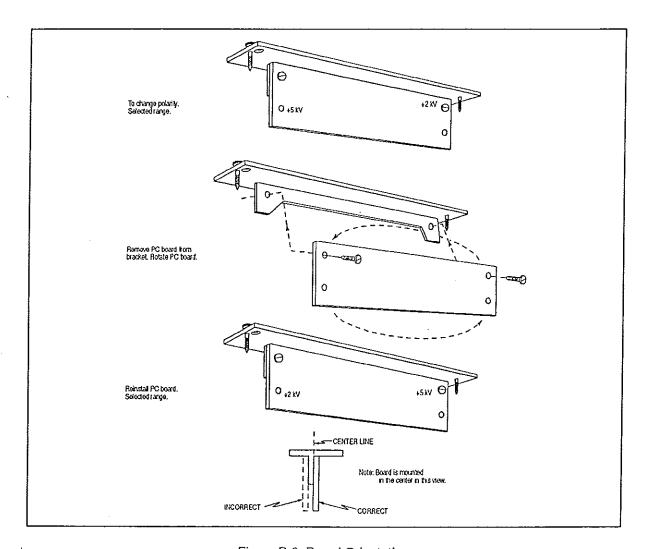

| Figure B.2 Board Orientation                                                                                                                                                                                    |                                      |

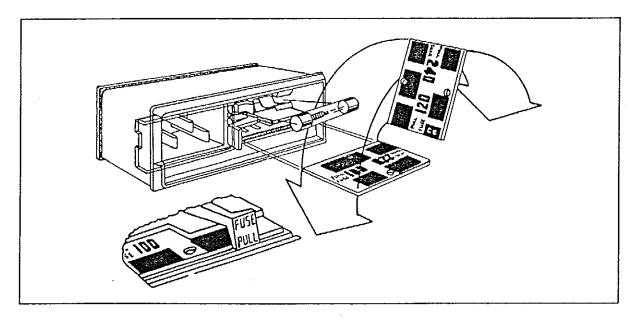

| Figure C.1 Voltage Selection                                                                                                                                                                                    | 34                                   |

| Figure C.3 Amplifier Internal Jumpers                                                                                                                                                                           | 35<br>36<br>38                       |

| Figure C.5 Model 1510-01 and Various MCAs                                                                                                                                                                       | 39                                   |

| Figure C.6 Model 1510-02 and AccuSpec/B or AccuSpec/MC                                                                                                                                                          | 39                                   |

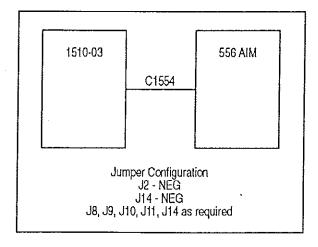

| Figure C.7 Model 1510-03 and Model 556 AIM                                                                                                                                                                      | 39                                   |

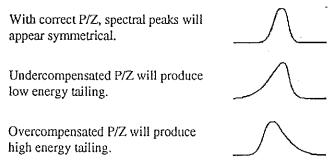

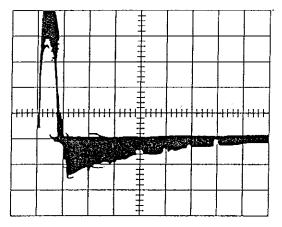

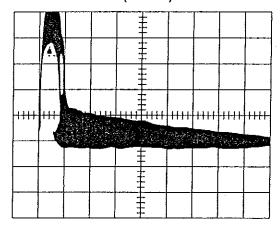

| Figure D.1 Correct Pole/Zero Compensation (Source)                                                                                                                                                              | 41                                   |

| Figure D.2 Undercompensated Pole/Zero (Source)                                                                                                                                                                  | 41                                   |

| Figure D.3 Overcompensated Pole/Zero (Source)                                                                                                                                                                   | 41                                   |

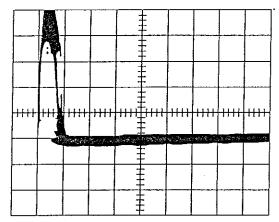

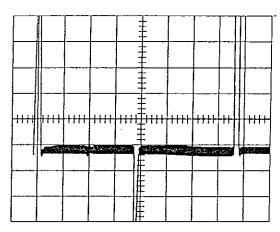

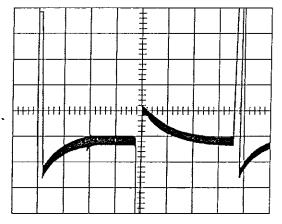

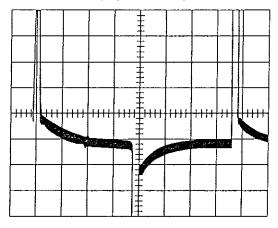

| Figure D.4 Correct Pole/Zero Compensation (Square Wave)                                                                                                                                                         | 41                                   |

| Figure D.5 Overcompensated Pole/Zero (Square Wave)                                                                                                                                                              | 41                                   |

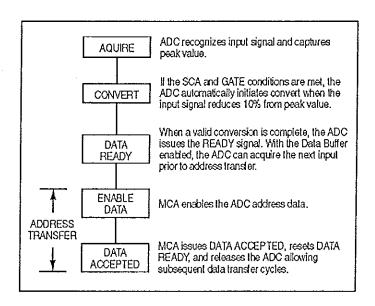

| Figure D.6 Undercompensated Pole/Zero (Square Wave) Figure F.1 Typical Conversion and Transfer Sequence                                                                                                         | 41                                   |

| Figure C. Evolcai Conversion and Transfer Segmence                                                                                                                                                              | 48                                   |

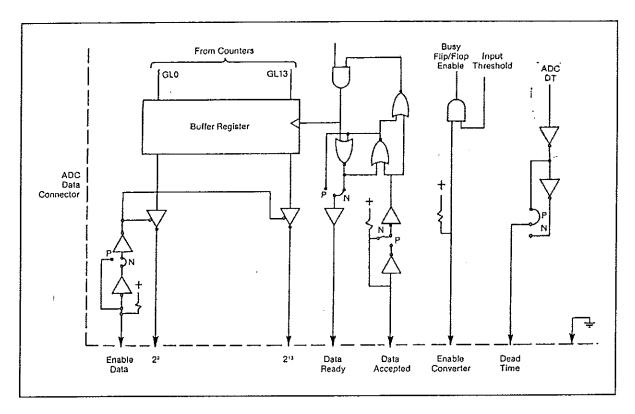

| Figure F.2 Representative Interfacing Logic    | 49 |

|------------------------------------------------|----|

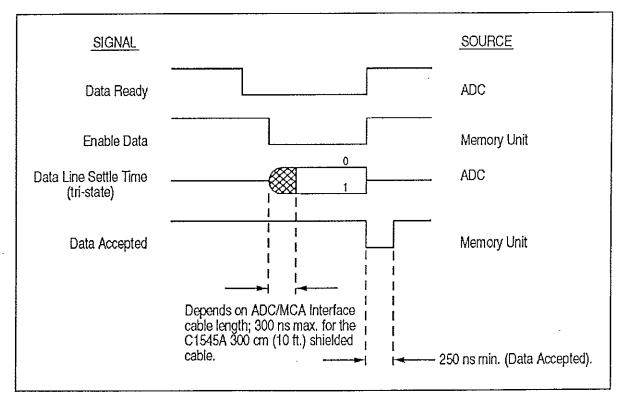

| Figure F.3 Data Transfer Timing Diagram        | 49 |

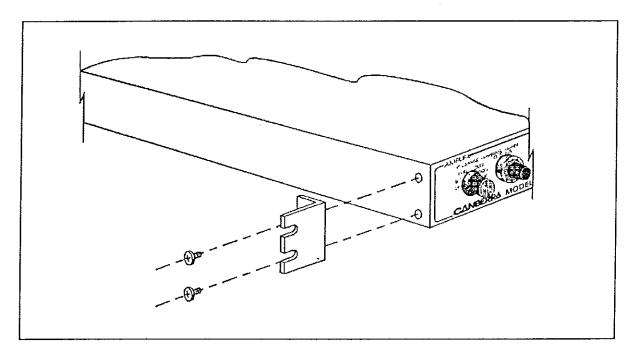

| Figure G.1 Installation of Rack Mount Hardware | 53 |

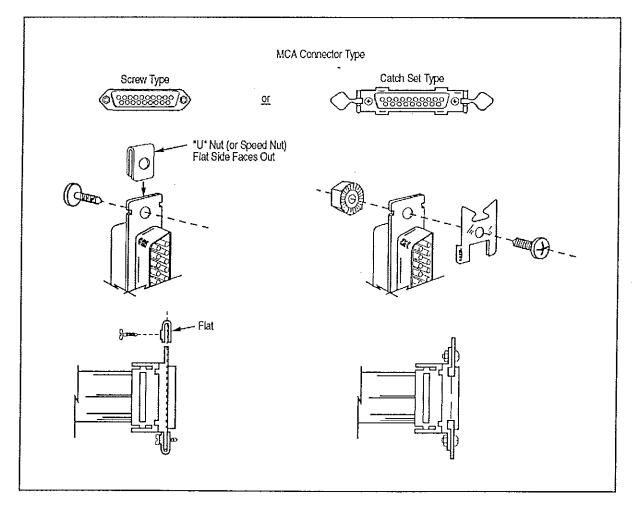

| Figure H.1 Connector Hardware Assembly         | 54 |

## 1. Introduction

The Canberra Model 1510 offers multichannel analyzer users research-grade front end signal conditioning and processing electronics in a low profile, self contained instrument. The 1510 is compatible with both conventional and PC-based multichannel analyzers.

The 1510 contains a high quality, high resolution spectroscopy amplifier with pile-up rejection and live-time correction, a 13-bit (8192 channel) Wilkinson-type ADC, and a versatile low noise bias supply suitable for use with all types of detectors. All components are integrated into a compact, low noise, EMI/RFI resistant chassis that is less than five cm (two in.) tall. The 1510 is suitable for bench mount, rack mount, or integration with personal computer based MCAs.

The 1510 is designed for spectroscopy applications in physics, education, environmental work, nuclear chemistry, and health physics. The advanced design ensures excellent performance in electronically noisy environments. Because of this, it is possible to place the 1510 between a Personal Computer chassis and a CRT monitor with little or no degradation in performance. Additionally, the 1510 has built-in protection against the most common types of ground loops that sometimes plague conventional high resolution systems.

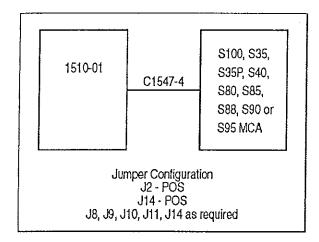

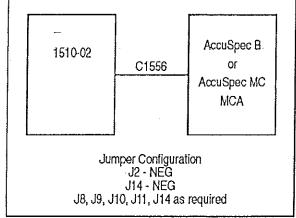

The 1510 ADC/MCA interface is jumper plug configurable for compatibility with all Canberra MCA products. To receive the 1510 properly configured for the intended Canberra MCA application, the configuration must be ordered using one of these three Model numbers:

| 1510-01 | The -01 option is for use with the Series 35, Series 35 Plus, Series 40, Series 80, Series 85, Series 88, Series 90, Series 95 and System 100 MCAs. |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1510-02 | The -02 option is for use with the AccuSpec/B and AccuSpec/MC MCAs.                                                                                 |

| 1510-03 | The -03 option is for use with the Model 556 Acquisition Interface Module (AIM).                                                                    |

## 1.1 High Voltage Bias Supply

The high voltage bias supply features low noise, low ripple and excellent stability. It accommodates all types of detectors providing either positive or negative bias at selectable regulated voltages of 15 to 2000 V dc at 1 mA or 30 to 5000 V dc at 300  $\mu$ A.

The bias supply will withstand an overload or a direct output short-circuit for an indefinite period and resume normal operation when the fault is removed. The output voltage may be turned On or Off remotely through the HVPS INH connector.

A convenient rear panel programming module provides selection of range and polarity. Polarity status is indicated by a front panel LED which can be previewed prior to activation of the power supply.

A front panel LED indicates an inhibit condition if the Bias Supply is inhibited by an LN<sub>2</sub> monitor or other external control.

## 1.2 Spectroscopy Amplifier

The amplifier provides unipolar shaping with active, complex-pole filter networks optimized for superior pulse symmetry, overload recovery, and signal to noise ratio ensuring the highest resolution and throughput. A wide choice of front panel selectable Shaping time constants (0.5, 1, 2, 4, 8 and 12 us) allows optimum matching of detector and count rate requirements.

A gated baseline restorer is employed with features and flexibility found only in top-of-the-line amplifiers. Automatic restorer rate and threshold remove the guesswork from setup ensuring optimal performance over a wide range of system and count rate conditions. Flexibility and performance are further enhanced with a choice of asymmetrical or symmetrical restoration.

Amplifier gain can be set precisely with the super fine gain control, which provides resolution better than 1 in 16 000 (0.006%).

The 1510 amplifier's exceptional dc stability, ultra low noise, optimum pulse shaping, and high performance baseline restorer offer uncompromising performance when used with germanium, Si(Li), scintillation, gas proportional, or silicon charged-particle detectors.

## 1.3 Pile-up Rejection/Live-time Correction

The Live-Time Corrector and Pile-Up Rejector allows quantitative gamma spectrum analysis nearly independent of system count rate. Special circuitry interrogates for pile-up and permits only those detector signals resulting from single energy events to be processed.

To compensate for rejected pulses and processing times, a system dead time is generated which extends the collection time by an appropriate amount.

A front panel LED is provided as a user aid when setting the PUR discriminator.

#### 1.4 ADC

The ADC is a Wilkinson type counter/ramp converter with a clock rate of 100 MHz, providing high throughput rate along with exceptional linearity and accuracy.

A direct-coupled input of 0 to 10 volts, provided by the 1510 or from an external amplifier, is digitized according to the front panel GAIN control into a binary code of 8 through 13 bits (256 through 8192 channels).

A choice of Pulse Height Analysis (PHA) or Sampled Voltage Analysis (SVA) are offered. Conversion in PHA mode is initiated automatically using an internal peak detector. The falling edge of a pulse applied to the ADC GATE input initiates the SVA conversion.

Conversions may be enabled or disabled by Coincidence/Anticoincidence gating or acceptance criteria programmed by the Lower Level (LLD) and Upper Level (ULD) discriminators.

Digital OFFSET and ADC RANGE can be employed to expand a portion of the input maintaining high resolution with limited memory.

The ADC is compatible with all Canberra MCAs and PC-based MCAs using the external interface options designated for each unit. The binary TTL-compatible interface logic can be set for positive (logic high) true or negative (logic low) true ensuring compatibility with many other MCA and memory systems.

# 2. Applications, Hardware and Accessories

The Model 1510 Integrated Signal Processor was designed to be easily incorporated into spectroscopy systems and applications providing high performance signal processing on a wide variety of MCAs. The 1510 configurations include: rack mounting, bench mounting, or integration into MCA/display systems between the MCA (conventional or PC-based) and its graphics display.

#### 2.1 Hardware and Accessories

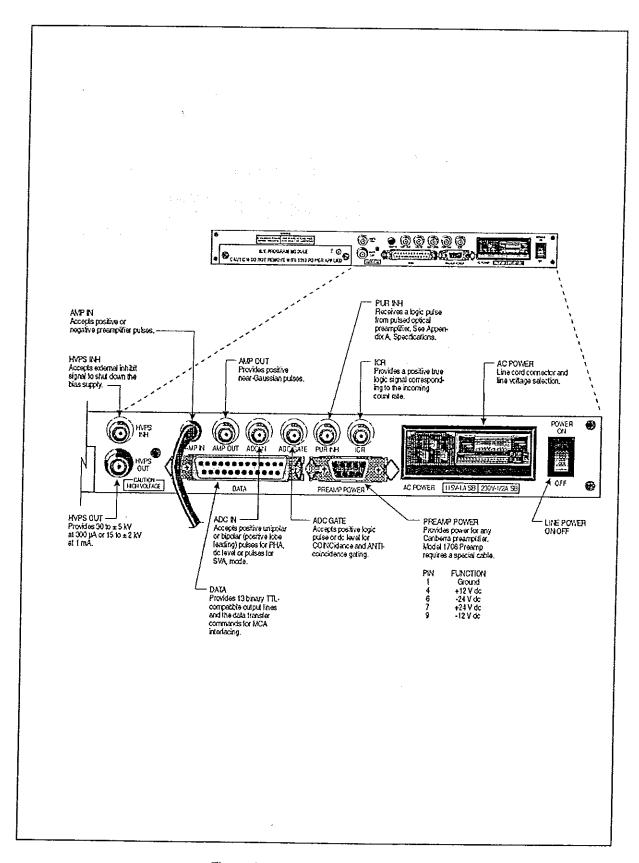

Accessories included with the 1510 for basic system integration and operation are: a line cord, an ADC to MCA interface cable, two 1.5 m (5 ft) BNC coax cables, one 0.2 m (0.5 ft) BNC coax cable, one 1.5 m (5 ft) SHV high voltage coax cable, one BNC barrel connector, one SHV barrel connector, one 1.5 m (5 ft) preamp power extender cable, and rack-mounting hardware.

## 2.2 Applications

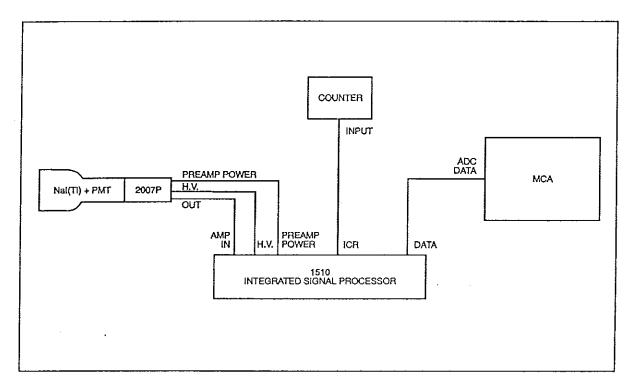

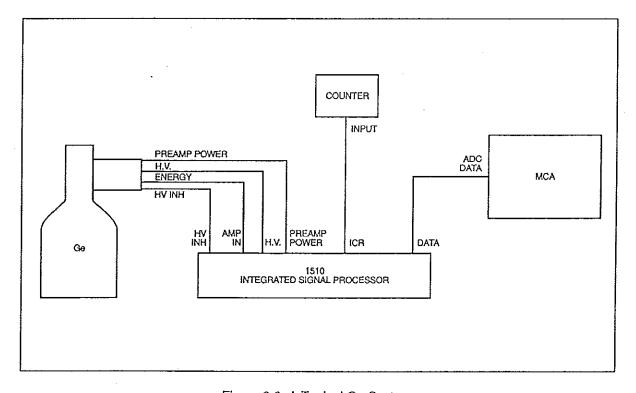

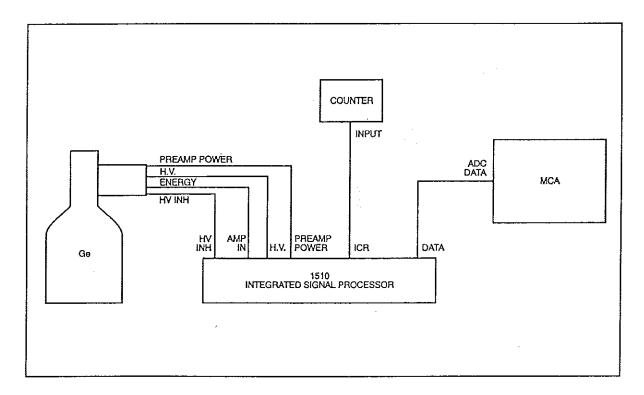

Figure 2.1 shows a typical application for a NaI(TI) Detector System and Figure 2.2 shows a typical Ge Detector System application.

The 1510 has been designed and engineered to operate in conventional and PC-based MCA system environments that use raster type monitors, conventional monochrome and enhanced color graphics types. When installed between the MCA and display as intended, it is subject to very intense magnetic and electrostatic noise.

The 1510 provides effective resistance to the effects of this most demanding application. However, careful attention must also be given to the low level signal cables external to the 1510 as ordinary coax cables offer little shielding from the effects of electromagnetic noise.

The AMP IN signal cable is a special 1.5 m (5 ft) flying lead cable terminated with a BNC connector. The SHV high voltage coax cable, HVPS INH, and preamp power extender cables are provided and installed to facilitate a neat cable assembly when connected to the detector cable set. The cables have been bundled together, maintaining maximum performance under these demanding EMI conditions.

The 1510 Amplifier's selection of shaping-time constants allows it to be used in surface barrier, PIPS proportional counter, NaI and Ge detector applications. The choice of shapings also allows the best possible performance by tailoring the system for the conflicting requirement of optimum signal-to-noise ratio and high count-rate performance. The excellent stability and low noise contribution enhances the use of this amplifier in most applications.

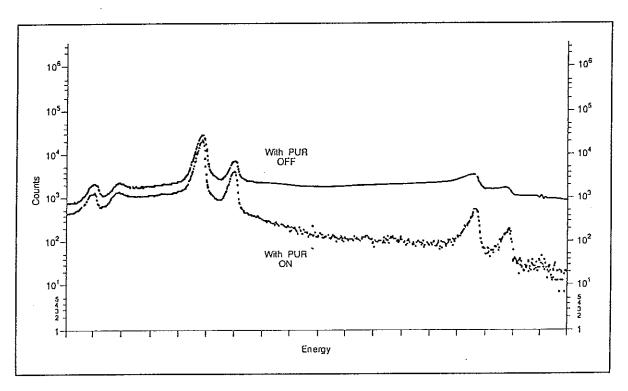

Nuclear spectroscopy with high count rates can be made more accurate by testing for pulse pileup and rejecting contaminated pulses. Pulse pileup produces distortions in the higher

ranges of the spectrum because successive shaped amplifier pulses tend to merge, and cause aberrations in the precise amplitudes as measured by the ADC. Since many spectra have higher count rates at the lower energies, the pileup of these pulses strongly affects the less intense higher energy counts and can result in significant errors. A pileup reject circuit provides substantial improvement to the spectrum.

If pulses are rejected from further analysis by the circuitry, the system is "dead" for some portion of time. It is customary to correct for dead or busy time in the ADC; this dead time should also be activated when a pileup reject circuit is operated with the ADC. The Model 1510 can extend the system dead time to compensate for pulses thrown away due to pileup rejection.

Typical applications are shown in Figure 2.1 for a system with a Ge detector and Figure 2.2 for a system with a NaI(Tl) detector.

Figure 2.1 A Typical NaI(TI) System

Figure 2.2 A Typical Ge System

## 3. Setup

. /

11

This section describes how to connect the system, how to set the internal controls, and how to select ac power and high voltage options.

## 3.1 Setting Internal Controls

Internal jumper plugs are provided for added flexibility and compatibility with all Canberra MCA products. Jumper plugs associated with the 1510 Spectroscopy Amplifier are factory set for general purpose applications. Jumper plugs associated with the ADC are factory set specific to the 1510 Model number and the intended Canberra MCA interface. The 1510 model numbers and MCA applications are listed below:

| 1510-01 | The -01 option is for use with the Series 35, Series 35 Plus, Series 40, Series 80, Series 85, Series 88, Series 90, Series 95 and System 100 MCAs. |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1510-02 | The -02 option is for use with the AccuSpec/B and AccuSpec/MC MCAs.                                                                                 |

| 1510-03 | The -03 option is for use with the Model 556 Acquisition Interface Module (AIM).                                                                    |

Please refer to Appendix C for jumper plug access and detailed information for your specific 1510 model.

## 3.2 Selecting the Proper AC Power Option

Power is applied to the Model 1510 with the rear panel ac power switch. Before applying power, check the voltage selection card inside the fuse compartment located on the rear panel. This is easily done by moving the plastic fuse shield to the left and looking directly under the fuse; the operating voltage will be visible. The 1510 is compatible with four line voltage ranges. Be sure that the fuse is compatible with selected line voltage. To select a different operating voltage, please refer to Appendix C.1.

## 3.3 Selecting the High Voltage Range and Polarity

High Voltage range and polarity are conveniently selected by the programming module located on the rear panel. The 1510's High Voltage Power Supply is factory set for the positive 30 to 5000 V (300 µA, max) range, which is compatible with most Ge detector applications. If your detector requires negative polarity and/or the higher current (1 mA, max; 15 to 2000 V range), refer to Appendix B for instructions. Please consult your detector's manual for its specific bias requirements.

CAUTION Excessive voltage and/or incorrect polarity can permanently damage the detector system.

The LEDs in the 1510's front panel HVPS section indicate polarity status when the 1510 is turned on and provide a polarity selection preview, whether the 1510 High Voltage Bias Supply is on or off.

Please refer to Appendix B for instructions on changing the 1510's high voltage polarity or voltage range.

## 4. System Integration and Connections

This section provides basic installation instructions for integrating the 1510 with the spectroscopy system's MCA and detector.

#### 4.1 Installation

Install the 1510 for the intended application: rack mount, bench mount or integration into an MCA graphics display system.

For rack-mount applications, the rack-mount hardware must first be installed, as described in Appendix G.

The instructions that follow will primarily focus on integration into MCA/graphics display systems using the System 100 or Series 95 MCAs and a Ge detector, with the 1510 on top of the MCA, between the MCA and the monitor.

#### 4.2 Cable Connectors

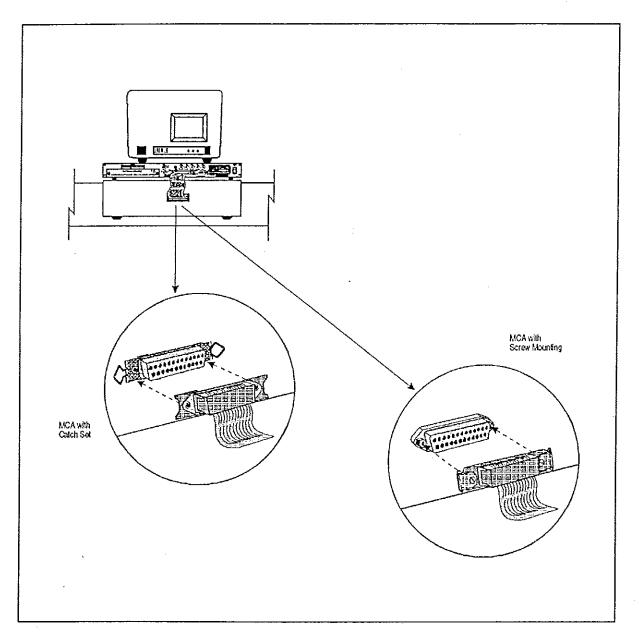

Before installing the C-1547-4 ADC/MCA interface cable, you must first determine which of two types of connector retaining methods is to be used (See Figure 4.1). The System 100 uses screws while the Series 90 and Series 95 use spring clips. To provide compatibility, both spring clips and screws have been included.

For retainer installation illustrations and instructions, please refer to Appendix H.

Note: It is not necessary to install the retaining hardware, but is advised to prevent an accidental disconnection during system operation.

## 4.3 Cabling

Install the ADC/MCA interface cable, connecting the data transfer link. The 1510 uses the spring clip retaining method. The ADC/MCA interface cable is 1.2 m (4 ft) long, which will accommodate most installations. If your installation requires a longer cable, an optional 3 m (10 ft) cable is available for the 1510-01.

Referring to Figure 2.1 as a guide for germanium detector systems, or to Figure 2.2 for sodium iodide detector systems, connect the 1510 cable assembly to the detector's preamplifier. For germanium detectors, note that the 1510's cable set connects to the detector's cable set, not to the preamplifier.

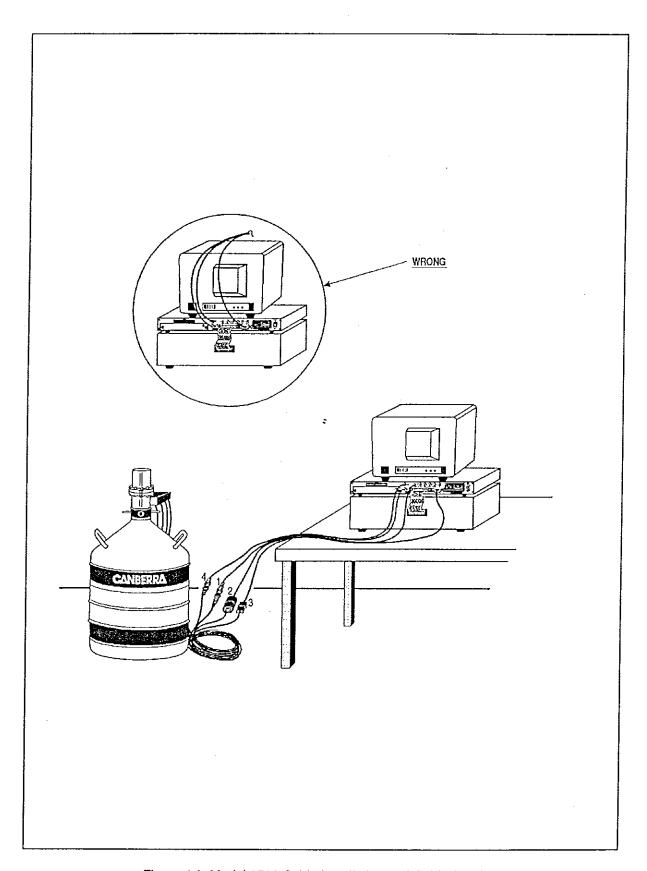

The 1510 cable set, shown in Figure 4.2, consists of the SHV high voltage cable (1), the AMP IN cable (2), the preamp power cable (3), and the HVPS INH cable (4). The figure also shows how the cable assembly must be routed away from the MCA system's monitor.

Note: Do not let the 1510 cable bundle get near the system's monitor as noise will be induced in the low level signal cables, degrading the 1510's resolution performance.

Verify that the 1510's adjacent rear panel AMP OUT and ADC IN signals are connected with the supplied  $0.5\ \mathrm{ft}$  BNC coax cable.

Figure 4.1 Attachment of ADC/MCA Interface Cable

Figure 4.2 Model 1510 Cable Installation and Cable Routing

## 5. Operation

This section outlines the operation of the Model 1510 Integrated Signal Processor. Following these procedures will make you familiar enough with the instrument to be able to use it effectively in most situations.

#### 5.1 Pre Turn-On

Verify that the High Voltage bias supply programming module is properly installed (see Section 3.3 and Appendix B). Please refer to your Detector's User's Manual for its required polarity and range.

Verify that the HV ON/OFF Switch is *off* and the VOLTAGE Control is set to 0.00 (fully counter-clockwise).

Verify that the 1510's ac input selection is compatible with the intended ac line power (see Section 3.2 and Appendix C.1).

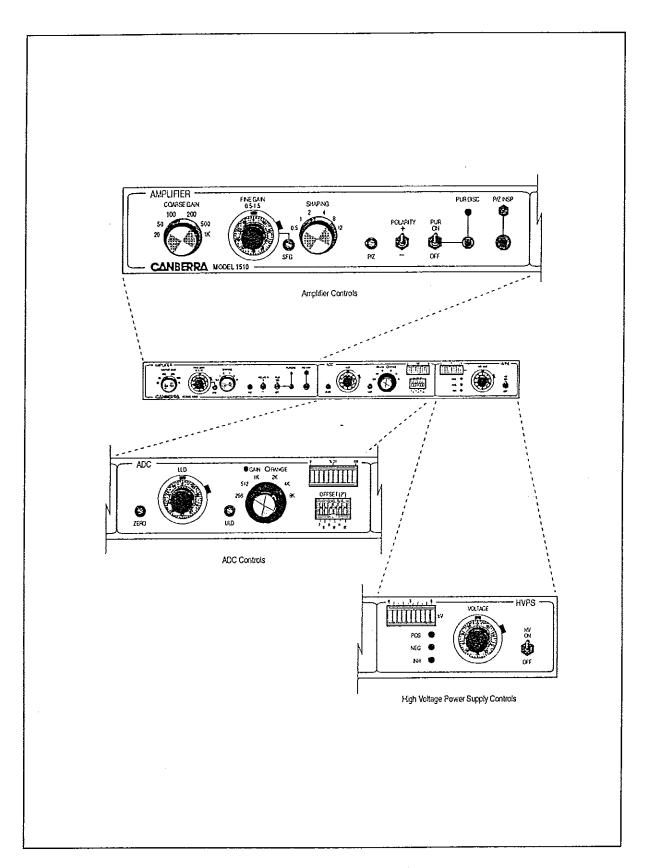

Connect the Model 1510 as shown in Figure 5.1 (the counter is optional).

Figure 5.1 PUR/LTC System Setup

#### 5.2 Turn On

Connect the 1510 to a compatible ac power source and set the 1510's rear panel Power On/Off switch to on.

Verify that the proper front panel High Voltage polarity LED (POS or NEG) is illuminated. The detector High Voltage bias polarity and range were previously selected in Section 5.1.

CAUTION Incorrect High Voltage bias and/or polarity can permanently damage the system's detector.

Verify that no segments of the High Voltage Indicator are illuminated.

Set the front panel HV ON/OFF Switch to on. The first segment of the High Voltage Indicator should now illuminate.

Note: Illumination of the High Voltage Indicator's first segment indicates that the high voltage supply is active.

Slowly increase the VOLTAGE control until the operating voltage of the system detector is attained.

The High Voltage Indicator should illuminate at 600 V per segment, showing the voltage present at the rear panel HVPS OUT connector.

Note: High Voltage control is provided by a direct-reading precision 10-turn dial. For the 5 kV range, the bias supply will respond up to 5.00 + 10%. The bias supply will limit and not respond to further increases of the dial's setting.

With the 2 kV range selected, the bias supply will likewise respond only up to 2.00 + 10%. Again, the supply will limit and not respond to further increases of the dial's setting.

## 5.3 Amplifier Setup

For a detailed explanation of the Amplifier's Front Panel Controls, please refer to Appendix A.1.3.

Set the amplifier controls as indicated below:

| Shaping     | • |  |  |  | - |   |  | ٠ |   | $4\mu s$ |

|-------------|---|--|--|--|---|---|--|---|---|----------|

| Coarse Gain |   |  |  |  |   | • |  |   |   | 100      |

| Fine Gain . |   |  |  |  |   | • |  |   | ٠ | 7.2      |

| PUR On/Off  |   |  |  |  |   |   |  |   |   | OFF      |

Set the amplifier Polarity switch to match the preamp's output polarity; positive (+) for a Canberra Model 2001 or 2002 preamp.

Place a radioactive source such as <sup>60</sup>Co near the face of the detector.

Monitor the amplifier output signal on the 1510 front panel P/Z Insp test point using a oscilloscope and scope probe. Connect the probe ground to the PUR ON/OFF switch body.

Semi-Gaussian shaped pulses approximately 9 V in amplitude should be observed when using a preamp gain of 100 mV/MeV and <sup>60</sup>Co radioactive source.

### 5.4 Pole/Zero (P/Z) Adjustment

For more detail on and an illustration of the P/Z adjustment procedure, please refer to Appendix D.1.

The P/Z trim is extremely critical for good high count-rate resolution performance. Adjust the radioactive source for a count rate between 2 kcps and 25 kcps.

Set the oscilloscope vertical sensitivity for 50 mV/div.

Press the inspect button while monitoring the amplifier's output at the 1510 front panel P/Z Insp test point with an oscilloscope. This will clamp the unipolar signal, preventing scope overload that might otherwise occur with the higher vertical sensitivity.

Adjust the Pole/Zero so that the trailing edge of the unipolar pulse returns to the baseline with no over- or under-shoots.

## 5.5 ADC Setup

For a detailed explanation of the ADC's Front Panel Controls, please refer to Appendix A.2.3.

Set the ADC GAIN and RANGE equal to the MCA's memory group size. For instance, set the ADC RANGE and GAIN to 4096 for an MCA with 4096 memory size.

Set the ADC controls as indicated below:

Lower Level Discriminator (LLD) . . . . 0.02 V (ccw)

Upper Level Discriminator (ULD) . . . . 10.5 (cw)

Digital Offset . . . . . . . . . . . all OFF

## 5.6 Spectroscopy Operation

Please refer to your MCA Operator's Manual for MCA operating directions.

Start MCA COLLECT with the <sup>60</sup>Co radioactive source previously placed near the detector. A spectrum should begin collecting on the MCA.

Note the % DT indicator. This 10-segment LED display shows the average dead time in increments of ten percent and will change proportionately with system count rate.

Adjust the Amplifier's COARSE GAIN so that the spectrum (data being displayed) is positioned conveniently on the display.

Use the Amplifier's SFG (Super Fine Gain) control when matching gains of several detectors or when establishing a specific gain (energy per channel). This control provides 100 times more resolution than the Fine Gain control.

### 5.7 PUR/LTC Operation

When selected, the 1510's PUR (PileUp Rejector) allows the ADC to convert only those detector signals resulting from single energy events. During the amplifier and ADC processing time, the Pileup Rejector inspects for pulse pileup and, when detected, initiates an ADC reject sequence, aborting the associated conversion process.

To compensate for dead time associated with rejected pulses and amplifier processing times, the Model 1510 generates a dead time signal which extends the collection time by the appropriate amount. The dead time signal is included in the MCA/ADC transfer signals and gates the MCA's live time clock.

The following instructions apply to obtain maximum performance when utilizing the Model 1510. Please refer to the operator's manuals regarding questions and use of the detector and MCA.

Connect the Model 1510 as shown in Figure 5.1 (the Counter is optional).

Set the 1510 Amplifier controls as follows:

| COAR   | SE GA | /I/ | ١. |  |  |  |  | - | ٠ | • |  | 300  |

|--------|-------|-----|----|--|--|--|--|---|---|---|--|------|

| FINE ( | GAIN  |     |    |  |  |  |  |   |   |   |  | 4.4  |

| POLA   | RITY  |     |    |  |  |  |  |   |   |   |  | (+)  |

| SHAPI  | NG .  |     |    |  |  |  |  | _ |   |   |  | 4 us |

Set the 1510 ADC controls as follows:

| GAIN   | 8 K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RANGE  | As required by MCA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| OFFSET | Equal to the MCA's memory size $% \left( 1\right) =\left( 1\right) \left( 1\right) $ |

| ULD    | Fully clockwise (+10.5 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Set the 1510 HVPS voltage and polarity compatible with detector requirements (see Section 3.3).

## 5.8 Performance Adjustments

- Monitor the 1510 amplifier output signal at the P/Z Insp test point and adjust the P/Z control (see Appendix D.1). The 122 keV <sup>57</sup>Co peak will be approximately 1.65 V in amplitude.

- 2. IMPORTANT! Remove all excitation sources from the vicinity of the detector.

- 3. Set the MCA to Collect.

- 4. Set the Model 1510 ADC'S LLD threshold just above the system noise level.

- 5. The following steps will optimize the discriminator sensitivity and insure that the discriminator threshold is set just above the noise level.

- a. Adjust the 1510 Amplifier PUR DISC control fully counterclockwise. The DISC LED indicator will continuously glow and the ADC's % Dead Time Indicator will show 100%.

- b. Adjust the PUR DISC control clockwise until the DISC LED indicator begins to blink.

- c. The PUR Discriminator Threshold is now properly set.

- 6. The % Dead Time Meter should now be at zero with only occasional flashing when a transient or spurious event is received.

- 7. IMPORTANT! If the Amplifier GAIN or SHAPING or the Detector or Preamplifier are changed, the PUR DISC control must be checked and possibly readjusted.

## 5.9 Incoming Count Rate (ICR)

With a nuclear counter connected to the 1510's rear panel ICR output, the average total input count rate can be monitored. The PUR must be set *on* and PUR Disc adjusted as in Section 5.8, step 5.

## 5.10 Pileup Rejection With a Live Source

- 1. Bring a source such as <sup>57</sup>Co near the detector. Adjust the source for an input count rate of approximately 50 kcps.

- 2. Set the MCA's memory to first half.

- 3. Set the MCA to Collect. Adjust the 1510's Amplifier gain to allow collection of the primary and sum peaks. If a gain adjust was necessary, readjust the PUR Disc as described in Section 5.8, step 5.

- 4. Set the MCA's preset to 60 Live seconds.

- 5. Disable Collect, clear Data, then re-enable Collect and accumulate a spectrum.

- 6. Set the MCA's memory to second half.

7. Accumulate a spectrum with the 1510 PUR ON/OFF switch off. Enable the MCA's Overlap function and compare the first half of the memory (PUR On) to that of the second half (PUR Off) (see Figure 5.2). Note the reduction in amplitude of both the sum peaks and the background. Also note the improved resolution of the sum peaks. The background reduction and improved resolution are directly indicative of the Pileup Rejector's capabilities, since only sum peak pulses which are indeed 100% in coincidence should be processed.

Figure 5.2 60Co Spectrum: PUR On vs. PUR Off

#### 5.11 Live Time Correction With a Live Source

Live time correction (LTC) may vary and is dependent on factors such as ADC type, ADC calibration, spectrum energy distribution and detector characteristics such as geometry, size and ballistic deficit.

To achieve the highest performance of the Live Time Corrector, it may be necessary to adjust the LLD control.

The amplifier and ADC work together, forming an integral system when performing PUR/LTC. As a result, performance is very dependent on the ADC and in particular on the ADC's LLD setting.

Normally, the ADC's LLD control is set just above the system noise level. This is required so that the ADC and the amplifier's PUR discriminator operate over the same signal dynamic

range. Note that setting the ADC's LLD control too low can cause undercorrection and setting it too high can result in overcorrection.

The reference peak area deviation should remain under 5% for system dead times up to 50%. If you want to improve the results, adjust the LLD control slightly and repeat the test outlined in steps 3 through 8, below.

The following LTC optimizing process assumes that source A is  $^{60}$ Co and source B is  $^{137}$ Cs. The 1173.2 keV peak of  $^{60}$ Co will be used as a reference. The upper peak, at 1332.5 keV, is not a good choice because a sum peak of  $^{137}$ Cs at  $2 \times 661.6 = 1323.2$  keV would interfere with the measurement.

- 1. Set up the equipment as indicated in Section 5.7.

- 2. Confirm performance adjustments indicated in Section 5.8.

- 3. Set the MCA's preset to 500 Live seconds.

- 4. Position radioactive source A near the Ge detector and adjust for an incoming count rate of 2 to 5 kcps. Once in place, the source should not be moved or altered in any way for the remainder of the experiment.

- 5. Collect a spectrum for 500 Live seconds.

- 6. To source A, add approximately 25 keps of source B to make the total incoming rate 30 keps.

**Note:** Each time the background (source *B*) is changed, allow the detector to stabilize a few minutes before collecting the spectrum.

- 7. Collect a new spectrum for 500 Live seconds and record the net area of source A.

- 8. Compare the net area in steps 5 through 7 and compute the percentage change.

- 9. If you feel improvement is desirable, try adjusting the LLD control 1% or 2% higher. Repeat steps 4 through 8 until an optimum setting is achieved.

- 10. Set the PUR ON/OFF switch to off. Repeat steps 3 through 8.

- 11. Compare the deviation of source A's spectrum when the PUR is on and the PUR is off.

Since the detector-source geometry was maintained and the preset Live Collection time was held constant, the <sup>60</sup>Co (1173.2 keV) net area can be used as a standard when comparing the effect of background (<sup>137</sup>Cs) count rate.

With the PUR off, large changes will be observed in the reference net peak area as a function of count rate. With the pileup rejector set on, changes in the reference peak net area will be significantly reduced. The Live Time corrector extends the collection time, compensating for amplifier processing time and events rejected due to pileup.

CAUTION The 1510's PUR/LTC function is integral to both the internal amplifier and ADC. It is possible to use the 1510 with

an external amplifier or ADC, but in this case the 1510's PUR must be switched *off*, to prevent possible system malfunction.

#### 5.12 ADC Gate

The GATE function allows the operator to enable or disable the ADC for acceptance and conversion of linear signals at its input. Depending on the criteria for the experiment in progress, the operator may use the GATE input in the factory-set Coincidence Mode or may change the function to the Anticoincidence Mode by moving a jumper on the ADC board (see Appendix C.5).

In order for the linear input signal to be considered by the ADC, it must be coincident in time with the GATE input signal.

A low logic level (0 to 0.8 V) at the GATE connector will disable the ADC. It will neither accept nor process any linear signals while the GATE is low.

A high logic level (2.5 to 5.5 V) at the GATE connector will enable the ADC. It will accept and convert all linear signals received while the GATE input is high.

If the GATE input is left open (unconnected), the ADC will act as if the GATE input is high and will accept and convert all linear signals received.

In the Anticoincidence mode, the logic is reversed. That is, a low logic level will enable the ADC and a high level (or an open input) will disable the ADC.

## 5.13 Sampled Voltage Analysis (SVA)

In the Sampled Voltage analysis (SVA) mode, analog voltages (dc or slowly changing ac voltages) can be sampled by the ADC, resulting in an amplitude distribution curve. The input signal must be between 20 mV and 10 V in amplitude and fall between the settings of the LLD and ULD controls to be considered.

The GATE input is used as the sampling signal, which must be coincident with the voltage to be sampled. Sampling occurs when the gate is high, conversion is initiated at the high to low transition.

The GATE sampling period or pulse width must be equal to or greater than 1 µs. However, for pulse inputs (rather than dc levels or slowly changing ac signals), the GATE input signal must be narrower than the input pulse width.

The sampling rate should be at least twice the frequency of the input signal for accurate sampling.

To use the Analyzer in the SVA mode, the factory set PHA/SVA jumper on the ADC board must be changed to the SVA position (see Appendix C.5). To return the Analyzer to the PHA mode, the jumper must be restored to the PHA position.

## 6. Circuit Description

This section describes the Model 1510 Integrated Signal Processor's circuits. Throughout the circuit description, please refer to the respective block diagrams.

### 6.1 Amplifier

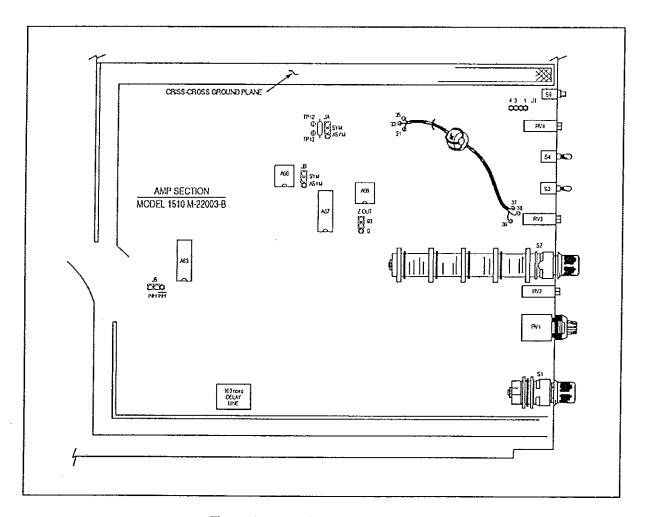

#### Block Diagram - Sheet 4

The input signal is accepted by the rear panel BNC and cable assembly, is differentiated by C110 through C114 and resistor R192. Pole/zero compensation is performed by potentiometer RV3 and resistors R186 through R190. The time constants are selected by shaping switch S2A and S2B.

The differentiated signal is amplified by AMP1, AMP2, and AMP3 or by AMP1 and AMP3 only, depending on the COARSE GAIN switch (S1) selection. The output of AMP3 drives active filter integrators A70 and A68 and the PUR/LTC circuit.

The active filters produce complex pole pairs providing pulse shape and a sharp frequency cutoff characteristic for optimal signal to noise ratio. The time constants are selected by the shaping switch section S2C, S2D, S2E, S2F and associated resistors and capacitors.

The output of the second integrator drives the unipolar output amplifier A71; the unipolar AMP OUT signal is provided on the rear panel BNC connector J105. Baseline restoration is performed by A67 and associated circuits. For optimum performance the restorer is gated off during an event and the restorer threshold is automatically set. The restorer gate signal also provides a timing reference for the pileup rejector circuit.

#### 6.1.1 Restorer

The baseline restorer uses a transconductance amplifier which develops a correction voltage at its output, is summed with the Unipolar Signal at A71, referencing the AMP OUT signal to 0 volts, maintaining the baseline.

The restorer symmetry is selectable using jumper plugs JA and JB. For the symmetrical restorer mode, positive and negative slew rates are equal. When asymmetrical is selected, the negative slew rate is reduced by a factor of 0.1, providing a softer restorer response for positive output signals.

#### 6.1.2 Restorer Gate and Auto Threshold

The Auto threshold circuit peak-detects the negative noise excursions of the AMP OUT signal, generating a positive reference equal to the average value of the AMP OUT noise level. This automatic reference voltage, proportional to the AMP OUT noise level, enables precision restorer gating.

Baseline correction is prevented during AMP OUTPUT signal intervals. Comparators A64 and A65 monitor the AMP OUTPUT signal and disable the baseline restorer when the restorer threshold is exceeded.

## 6.2 Pileup Rejection

#### Block Diagram - Sheet 2

The Pileup Rejector (PUR) monitors the number of amplifier input events during a pulse processing sequence, which starts with an AMP IN signal and ends when the AMP OUT signal returns to the baseline. If two or more events occur during a processing sequence and the ADC is in the acquisition mode, Linear Gate (LG) is set true, the events are considered to be piled up and the pending ADC conversion is aborted.

The signal from gain amp A3 is shaped and discriminated from noise by the PUR discriminator. A fast timing pulse (system trigger) is produced for input signals that exceed the PUR DISC threshold.

The system trigger simultaneously clocks the Busy and Reject flip-flops. For the case of no pileup, only the Busy flip-flop will get set, since the "D" input of the Reject flip-flop was initially false. However if a subsequent AMP IN signal arrives before the conclusion of the processing sequence (pileup) the Reject flip-flop and REJECT signal will be set true. If the ADC is in the acquisition mode (LG true), a Reject will initiate an ADC reject sequence, the pending ADC conversion will be aborted and the events thrown away. At the conclusion of the processing sequence, the AMP OUT signal returns to the baseline and the training edge of the restorer gate signal clears the Busy and Reject flip-flops.

#### 6.3 Live Time Correction

#### Block Diagram - Sheet 2

Live time correction is accomplished by extending the collection time (stopping the MCA live time clock) for the AMP OUT signal processing time, as determined by the busy and the Dead Time Extension (DTE) flip-flops, to allow replacement of events thrown away in the event of pileup.

Piled up events will produce multiple system triggers within the processing sequence. As before, the first trigger sets the Busy flip-flop, and the second trigger sets the Reject flip-flop. Reject is set true and the ADC aborts the conversion in process. The ADC Linear Gate (LG) ends prematurely and its positive transition clocks the DTE (Dead Time Extension) flip-flop true, adding a dead time component to the ADT signal via the OR gate.

When the AMP OUT signal returns to the baseline, the Busy and Reject flip-flops are cleared as before. However, the DTE flip-flop remains set and its Dead Time contribution continues.

For the next non-piled up processing sequence, the Reject flip-flop will not be set and the positive transition of the associated ADC LG signal will clock the DTE flip-flop reset, ending its dead time contribution. At the conclusion of the AMP OUT signal, the Busy flip-flop is cleared, ending its dead time component. When the sequence has ended, the ADT signal goes false and the MCA Live Time clock resumes.

## 6.4 Analog-To-Digital Converter (ADC)

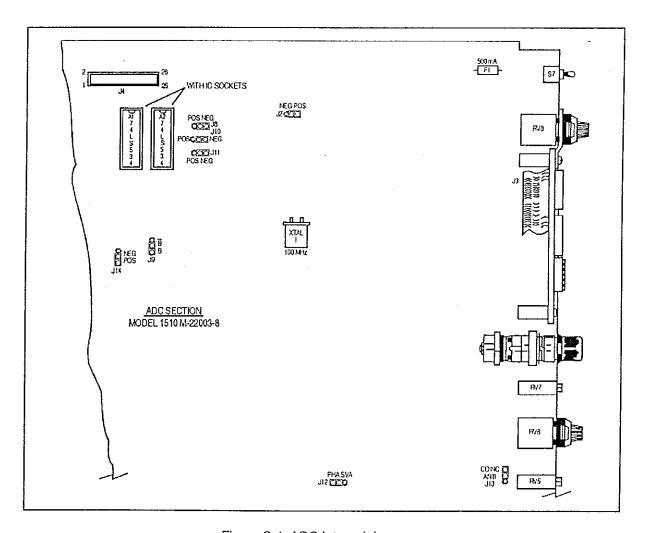

#### Block Diagram - Sheet 3

The 1510 ADC is a Wilkinson-type ADC; the input signal is captured on a holding capacitor and discharged at a constant rate while counting clock pulses into a address register.

Prior to the acquisition mode, the ADC stretcher is normally active and will track and follow signals present at the input. If no conversions are in progress and the input signal threshold is exceeded, the Busy flip-flop will get set. Linear Gate (LG) is enabled, indicating the ADC is acquiring a signal and the stretcher will now peak-detect the corresponding input signal. When the input signal reduces to 90% of its peak value, and if the SCA and coincidence requirements are met, a conversion will be initiated. The start convert flip-flop is set, the Linear Gate (LG) closes, and the ADC conversion begins.

The precision ramp-down current source and counters are synchronously enabled. A binary counter, driven by a 100 MHz clock, is enabled for the duration of the ramp down sequence. When the stretcher voltage reaches the ADC "zero" reference, the ramp and counters are gated off, ending the conversion. The resultant digital address in the counter represents the magnitude of the ADC input.

The converted address is loaded into the tri-state bus drivers and DATA READY request is set, initiating data transfer.

In response to DATA READY, the MCA or computer sets ENABLE DATA true, which activates and enables the tri-state bus drivers allowing the ADC address to be presented on the data bus. At the conclusion of the Data Storage Cycle, DATA ACCEPTED is enabled clearing the DMA Ready flip-flop.

If the pulse was not within the LLD/ULD window, or if the GATE criterion was not met or REJECT was set, the stretcher ramp down sequence would have been aborted. The stretcher capacitor would be reset; that is, quickly discharged to prepare for a new input.

## 6.5 High Voltage Power Supply (HVPS)

#### Block Diagram - Sheet 1

The High Voltage Power Supply provides positive and negative 15 to 2000 volts and 30 to 5000 volts. The polarity and range are determined by the programming module which selects a half wave rectifier or voltage tripler network and the polarity orientation of the respective rectification/multiplier networks.

The dc/dc inverter runs at a natural frequency of approximately 30 kHz, determined by the primary's inductance and capacitance.

The output voltage is proportional to the inverter input control voltage provided by Integrator A78D. The output voltage is sampled, attenuated, fed back, and compared with a fraction of the reference voltage determined by A77 and the HV voltage control. Integrator A78D drives the dc/dc inverter until the output voltage matches the selected reference.

Current limiting is provided by comparators A79B and A79C. When a fault or overcurrent condition is sensed, the comparator output disables the dc/dc inverter input control voltage.

## 6.6 Low Voltage Power Supply (LVPS)

The Low Voltage Power Supply provides +5 V,  $\pm$  12 V and  $\pm$  24 V. It is a conventional linear supply using full wave rectifiers from an ac tapped transformer with capacitive input filters. Three-terminal regulators provide each of the regulated supply voltages. Each of the supplies is factory calibrated using potentiometers RV19 through RV23.

## A. Specifications

## A.1 Spectroscopy Amplifier

#### A.1.1 Inputs

AMP IN - Accepts positive or negative tail pulses from an associated preamplifier; amplitude  $\pm 10$  V divided by the selected gain,  $\pm 12$  V maximum; rise time: less than shaping time constant; decay time constant:  $40 \,\mu s$  to  $\infty$ ;  $Z_{in} \approx 750 \,\Omega$ ; rear panel BNC connector and 1.5 m (5 ft) cable assembly.

PUR INH - Receives a standard TTL logic signal from associated reset preamplifier; extends the Dead Time signal, inhibit and reset the pileup rejector during the preamplifier's reset cycle; positive true or negative true internally selectable; rear panel BNC connector.

#### A.1.2 Outputs

AMP OUT - Provides positive, linear, actively filtered, near-Gaussian shaped pulses; amplitude linear to + 10 V, 12 V max.; dc restored; output dc level factory calibrated to  $0\pm5$  mV;  $Z_{out}$  <1  $\Omega$  or  $\approx$  93  $\Omega$  internally selectable; short circuit protected; rear panel BNC connector.

ICR (Incoming Count Rate) - Provides a standard TTL logic signal; frequency corresponds to input count rate; positive true; width  $\approx 150$  ns,  $Z_{out} \approx 50 \Omega$ ; rear panel BNC connector.

#### A.1.3 Front Panel Controls

COARSE GAIN - Six-position rotary switch selects factors of X20, X50, X100, X200, X500 and X1000.

FINE GAIN - Ten-turn locking dial precision potentiometer selects variable gain factor of X0.5 to X1.5; resettability  $\leq 0.03\%$ .

SFG (super fine gain) - Multi-turn screwdriver potentiometer selects gain with an adjustment resolution of better than 1 in 16 000 (0.0063%).

POLARITY - Two-position toggle switch sets the amplifier for the polarity of the incoming preamplifier signal.

P/Z - Multi-turn screwdriver-adjustable pole/zero potentiometer optimizes amplifier baseline recovery and overload performance for the preamplifier's fall time constant and the amplifier's chosen shaping time; range:  $40 \mu s$  to  $\infty$ .

P/Z INSP - Momentary pushbutton switch clamps the AMP OUT signal viewed on the test point to approximately ±300 mV, minimizing scope overload for precise pole/zero adjustment.

SHAPING - Six-position rotary switch; providing 0.5, 1, 2, 4, 8 and 12 µs shaping time constants.

PUR ON/OFF - Two-position toggle switch enables (ON) or disables (OFF) the pileup rejector and live-time corrector.

PUR DISC - Multi-turn screwdriver adjustable potentiometer optimizes the pile-up rejector discriminator threshold level; provides a variable range of 0 to 500 mV; LED indicator aids in setting the threshold.

#### A.1.4 Internal Controls

INH/-INH - Jumper plug selects PUR INH polarity compatibility; factory set for positive true logic.

ASYM-SYM - Jumper plug selects ASYMmetrical or SYMmetrical baseline restorer modes; factory set to SYMmetrical.

AMP  $Z_{OUT}$  - Jumper plug provides  $Z_{out} < 1 \Omega$  or  $\approx 93 \Omega$ ; factory set for  $< 1 \Omega$ .

#### A.1.5 Performance

#### **Amplifier**

GAIN RANGE - Continuously variable from X10 to X1500.

OPERATING TEMPERATURE - 0 to 33 °C.

GAIN DRIFT - ≤±0.0075%/°C, after a 30 minute warm-up.

DC LEVEL DRIFT - ≤±10 µV/°C, after a 30 minute warm-up.

INTEGRAL NON-LINEARITY - ≤±0.05%, over total output range for 2 µs shaping.

OVERLOAD RECOVERY - Recovers to within  $\pm 2\%$  of full scale output from X1000 overload in 2.5 non-overloaded pulse widths, at full gain, any shaping time constant, with pole-zero cancellation properly set.

NOISE CONTRIBUTION -  $\le$ 4.0  $\mu$ V true rms referred to input, 2  $\mu$ s shaping, and amplifier gain  $\ge$ 100.

PULSE SHAPING - Near-Gaussian shape: one differentiator, two active filter integrators; time to peak: 2.35X shaping time; pulse width: 7.3X shaping time; time to peak and pulse width measured at 0.1% of full scale output.

RESTORER - Active gated.

UNIPOLAR COUNT RATE STABILITY - For 2 µs shaping, the FWHM of a <sup>60</sup>Co 1.33 MeV gamma peak for an incoming rate of 2 kcps to 100 kcps and 9 V pulse height will typically change less than 14%; the peak position will typically shift less than 0.024%.

Note: These results may not be reproducible if the associated detector exhibits an inordinate amount of long rise time signals.

#### Pileup Rejector/Live Time Corrector

PULSE PAIR RESOLUTION - <500 ns.

MINIMUM DETECTABLE SIGNAL - Limited by detector/preamp noise characteristics.

#### A.2 100 MHz ADC

#### A.2.1 Inputs

ADC IN - Accepts positive unipolar or bipolar (positive lobe leading) pulses; amplitude 0 to + 10 V, + 12 V maximum; rise time 0.25 to 100  $\mu$ s maximum; width 0.5  $\mu$ s minimum;  $Z_{in} = 1$   $k\Omega$ ; direct coupled; rear panel BNC.

ADC GATE - Internal jumper plugs provided for selecting Coincidence/Anti-coincidence and PHA/SVA. PHA Mode: With Coincidence (Anti-coincidence) selected, a positive (negative) TTL level during the time-to-peak interval will enable conversion and storage of pulse, logic low (high) level will cause pulse to be rejected. Sampled Voltage Analysis (SVA) Mode: GATE IN used as a sampling signal; accepts positive TTL logic pulse or dc level; SVA pulse width  $\geq 1~\mu s$ ; Coincidence/SVA loading: 4.7 k $\Omega$  pull-up resistor to + 5 V; rear panel BNC connector.

#### A.2.2 Outputs

DATA - Provides 13 binary TTL-compatible output lines and the data transfer commands required for MCA interface; rear panel 25-pin D-type connector. Data Lines are negative true unless specified for positive true.

#### A.2.3 Front Panel Controls

GAIN - Six-position rotary switch selects full scale resolution of input signal; selection of 256, 512, 1K, 2K, 4, or 8K channels for a 10 V input pulse.

RANGE - Six-position rotary switch selects 256, 512, 1024, 2048, 4096 or 8192 channels as the overflow limit.

OFFSET - Six DIP switches to provide suppression of the digital zero; 0 to 8064 channels in multiples of 128 channels.

LLD - Ten-turn locking-dial precision potentiometer sets the Lower Level Discriminator for minimum input acceptance voltage; range 0.02 to + 10 V dc.

ULD - Screwdriver adjusted multi-turn potentiometer sets the Upper Level Discriminator for maximum input acceptance voltage; range 0.02 to + 10.5 V dc.

ZERO - Screwdriver adjusted multi-turn potentiometer sets the ADC's analog zero intercept level; range  $\pm 5\%$  of input range; resolution 0.005% of full scale.

#### A.2.4 Internal Controls

DATA BUFFER ENABLE/DISABLE - Jumper plug to enable or disable data buffer; factory set to enable.

ENABLE CONVERTER POS/NEG - Factory set to the ordered configuration.

SVA/PHA - Jumper plug selects PHA or SVA; factory set to PHA.

COIN/ANTI - Jumper plug selects coincidence or anti-coincidence gating for PHA mode; factory set to coincidence.

Four jumper plugs selects the polarity of the MCA transfer commands:

DT POS/NEG - Factory set to the ordered configuration.

READY POS/NEG - Factory set to negative true.

DATA ACCEPTED POS/NEG - Factory set to negative true.

ENABLE DATA POS/NEG - Factory set to negative true.

#### A.2.5 Indicators

%DT - Ten-segment LED indicator displays the average dead time of the converter.

#### A.2.6 Performance

INTEGRAL NON-LINEARITY -  $<\pm0.025\%$  of full scale over the top 99.5% of range including effects from tilt.

DIFFERENTIAL NON-LINEARITY - <±0.7% over the top 99.5% of range.

DRIFT, GAIN - <±0.009% of full scale/°C, after a 60 minute warm-up.

DRIFT, ZERO - <±0.0025% of full scale/°C, after a 60 minute warm-up.

DRIFT, LONG TERM - <±0.005% of full scale per 24 hours at a constant temperature.

PEAK SHIFT - <±0.025% of full scale at rates up to 50 kHz.

ADC DEAD TIME - Linear Gate Time + Conversion Time + Memory Cycle Time.

CONVERSION TIME - 1.5  $\mu$ s + 0.01 (N + X)  $\mu$ s where N = Address Count, and X = effective digital offset.

CHANNEL PROFILE - Typically flat over 90% of channel width.

## A.3 High Voltage Bias Supply

#### A.3.1 Inputs

HVPS INH - Logic low inhibits and gates off the output high voltage; maximum logic low  $\le 0.7 \text{ V}$  at  $\le 1.3 \text{ mA}$ : Open circuit or logic high  $\ge 6 \text{ V}$  resumes normal operation; sourcing: 12 V through  $10 \text{ k}\Omega$ ; maximum input + 12 V; rear panel BNC.

#### A.3.2 Outputs